Bruce Jacob

University of Maryland ECE Dept.

SLIDE 1

### ENEE 359a Digital VLSI Design

### **Static CMOS Logic**

#### Prof. Bruce Jacob blj@eng.umd.edu

Credit where credit is due:

Slides contain original artwork (© Jacob 2004) as well as material taken liberally from Irwin & Vijay's CSE477 slides (PSU), Schmit & Strojwas's 18-322 slides (CMU), Wolf's slides for *Modern VLSI Design*, and/or Rabaey's slides (UCB).

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 2

### **Overview**

- General complementary logic design,

perspective, stick-figure circuit diagrams

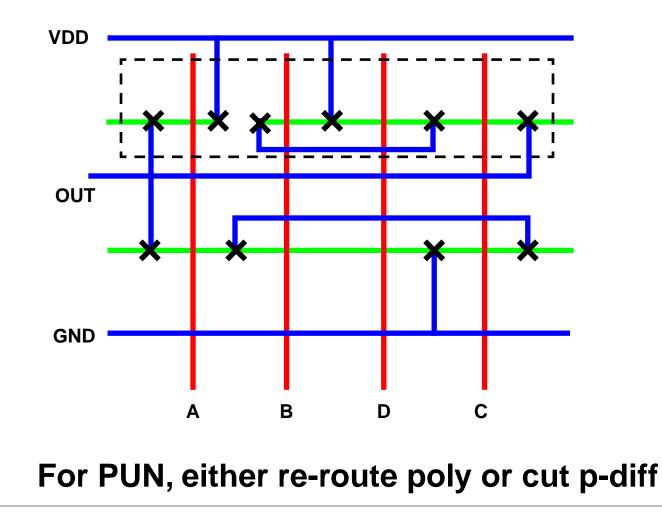

- Examples: constructing PDN/PUN duals, logic -> circuit, circuit -> logic, circuit -> layout, layout -> circuit, cross sectional views of layout

| ENEE 359a<br>Lecture/s 6+7<br>Static CMOS Logic       | Building Blocks                                                                     |

|-------------------------------------------------------|-------------------------------------------------------------------------------------|

| Bruce Jacob<br>University of<br>Maryland<br>ECE Dept. | NMOS devices in series<br>implement a NAND function                                 |

| SLIDE 6                                               | $A \longrightarrow B$                                                               |

|                                                       | NMOS devices in parallel<br>implement a NOR function<br>$output = \overline{A + B}$ |

| UNIVERSITY OF MARYLAND                                |                                                                                     |

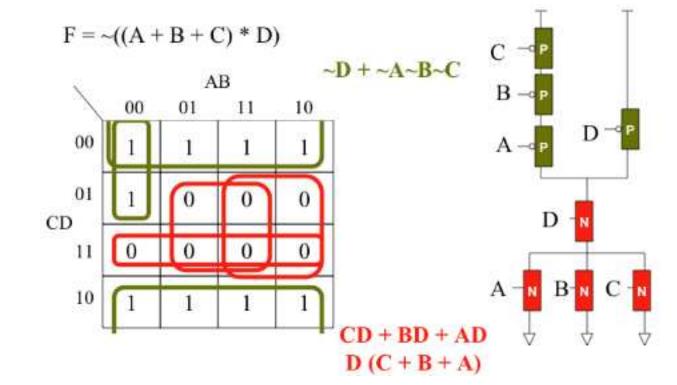

# **Implements Arbitrary Logic**

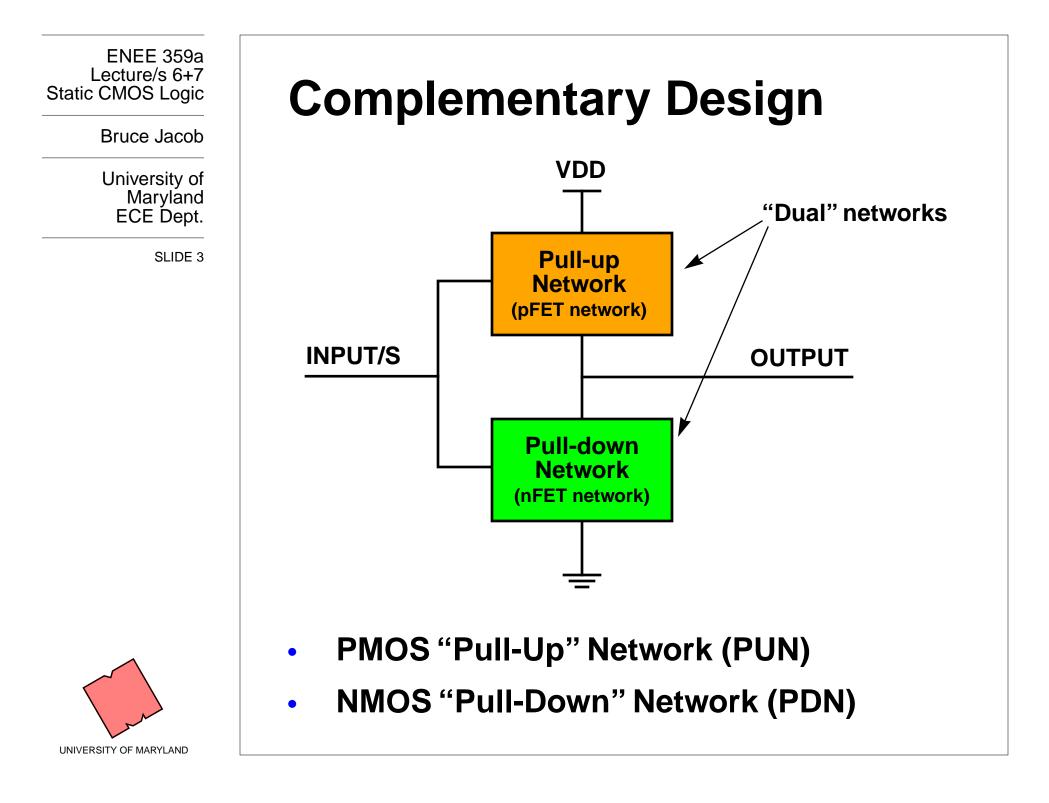

- Pull-Up Network: on when function = 1

- Pull-Down Network: on when function = 0

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 8

# **Static CMOS: Perspective**

- "Static" as in "output is logic function of inputs, and, given stable inputs, it does not change over time"

- Propagation delay function of load capacitance and resistance of transistors

#### **PROS**:

- Full rail-to-rail swing; high noise margins

- Logic levels not dependent upon relative device sizes

- Always a path to Vdd or Gnd in steady state; low output impedance

- Extremely high input resistance; nearly zero steady-state input current

- No direct path steady state between power and ground; no static power dissipation

#### CONS:

- UNIVERSITY OF MARYLAND

- N inputs => 2N transistors in design

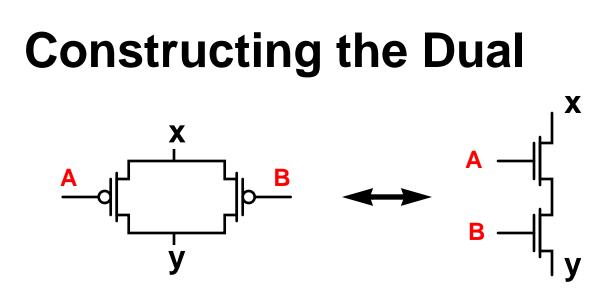

Transistors in parallel are in series in dual; transistors in series are in parallel in dual

This is the physical realization of DeMorgan's theorems:

- $\overline{A + B} = \overline{A} \cdot \overline{B}$  [!(A + B) = !A !B or !(A | B) = !A & !B]

- $\overline{A \bullet B} = \overline{A} + \overline{B}$  [!(A B) = !A + !B or !(A & B) = !A | !B]

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 10

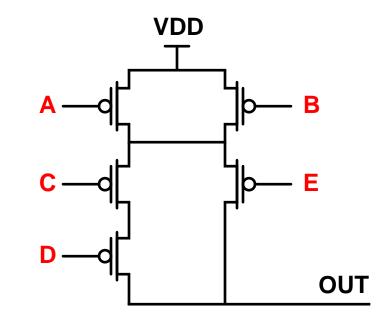

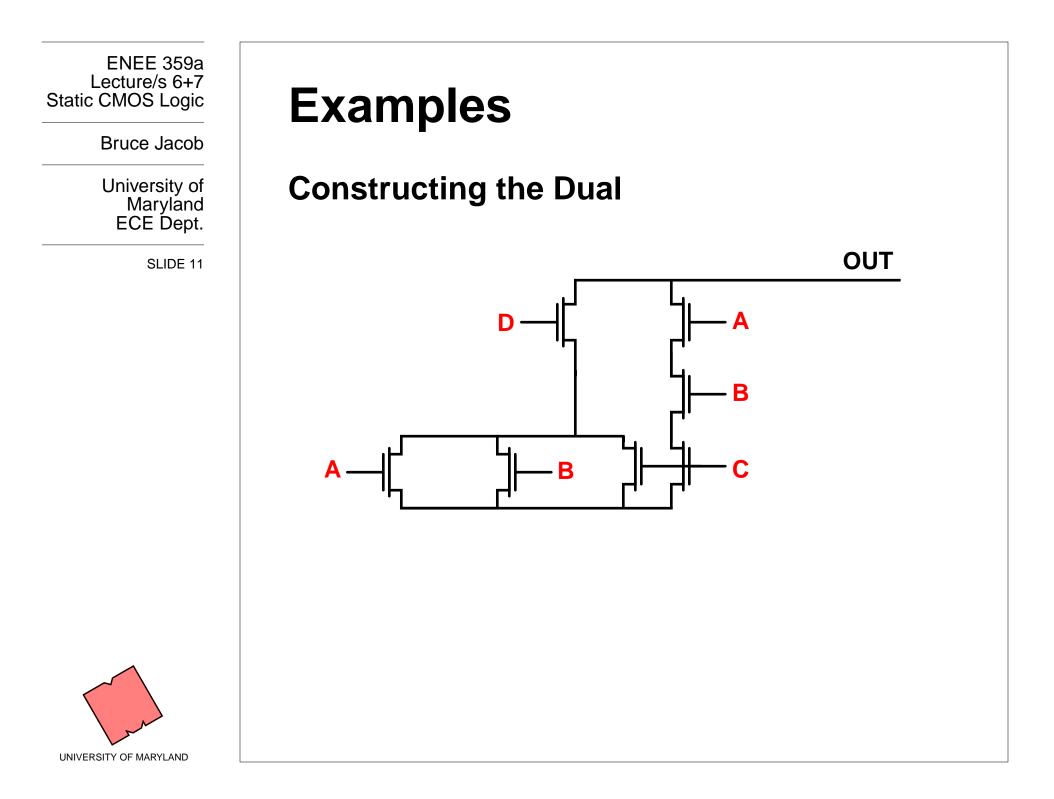

### **Examples**

#### **Constructing the Dual**

#### Bruce Jacob

University of Maryland ECE Dept.

SLIDE 12

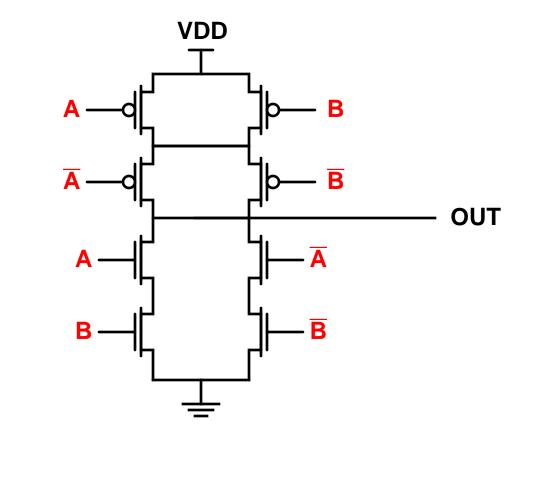

### Examples: Logic <-> Circuit

XOR [ out = ~( A B + A B ) ]

### Examples: Logic <-> Circuit

XOR [ out = ~( A B + A B ) ]

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

#### Bruce Jacob

University of Maryland ECE Dept.

SLIDE 14

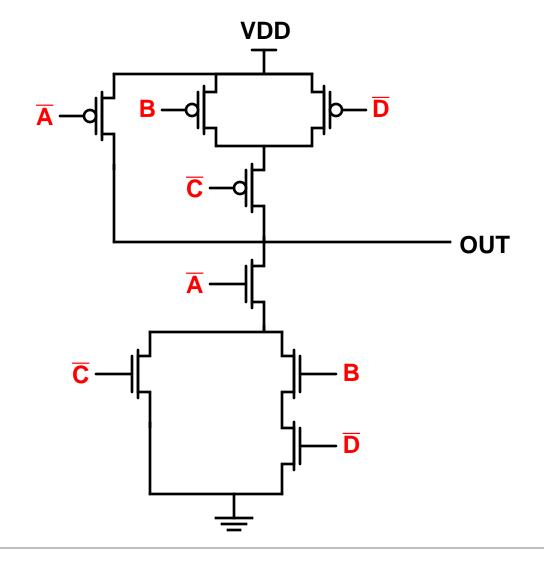

## Examples: Logic <-> Circuit

out =  $\sim$ ( $\overline{A} \cdot (\overline{C} + B\overline{D})$ ) •

## Examples: Logic <-> Circuit

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 16

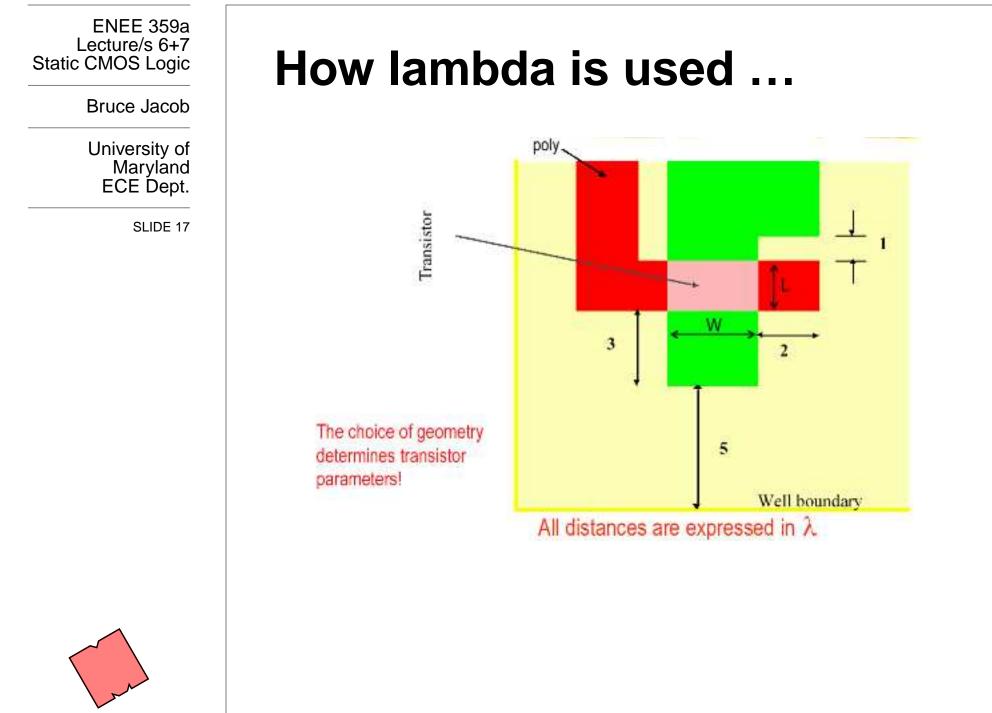

# SCMOS

### **SCALABLE DESIGN RULES**

#### **CMOS Scales Well ... Exploit That Fact**

- Implement it now, shrink it later

- Express all design rules in terms of unit dimension

- Change dimension of the unit, whole design shrinks

- Mead & Conway

#### Unit Dimension: Minimum Line Width (2λ)

- In 1978,  $\lambda = 1.5 \mu m$  (a.k.a. 3 micron technology)

- In 2004,  $\lambda = 0.045 \mu m$  (a.k.a. 90 nanometer technology)

#### Important Intellectual Idea (but not used in industry) (but we will)

(why not? elegance costs \$\$\$ ... currently *thousands* of design rules)

UNIVERSITY OF MARYLAND

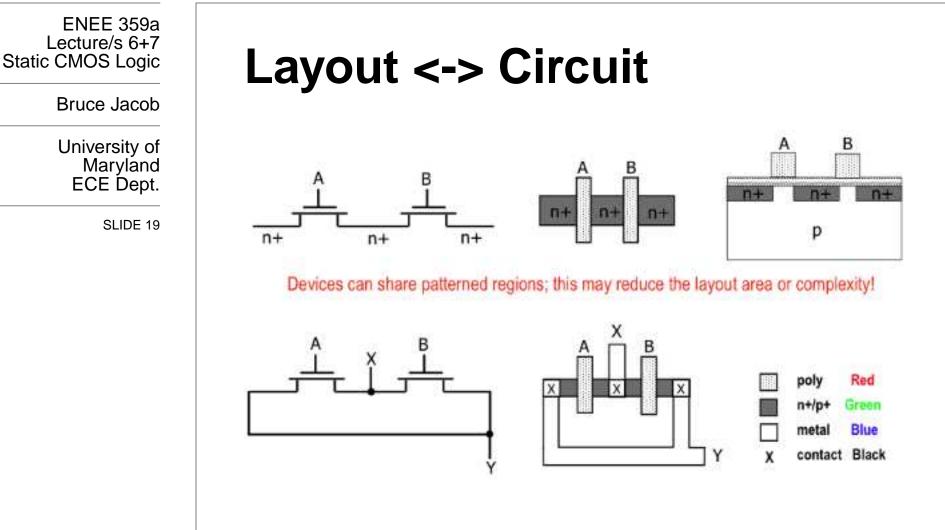

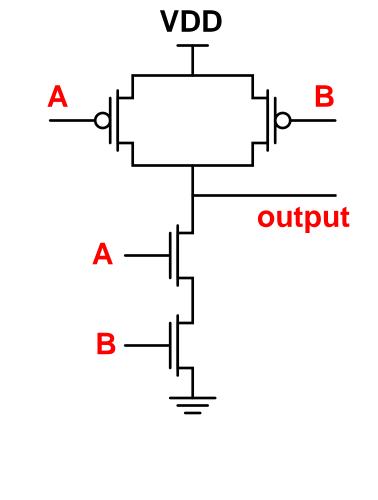

- FETs in series: source-drain overlap

- FETs in parallel: can share source/drain

Bruce Jacob

University of Maryland ECE Dept.

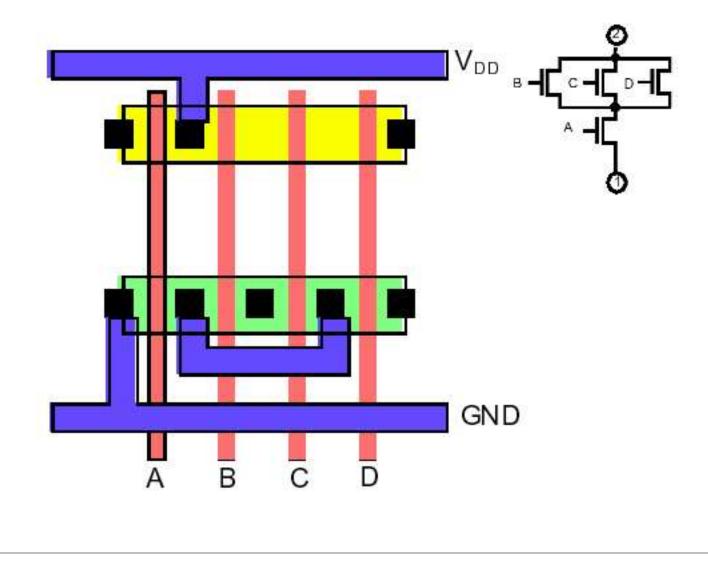

SLIDE 20

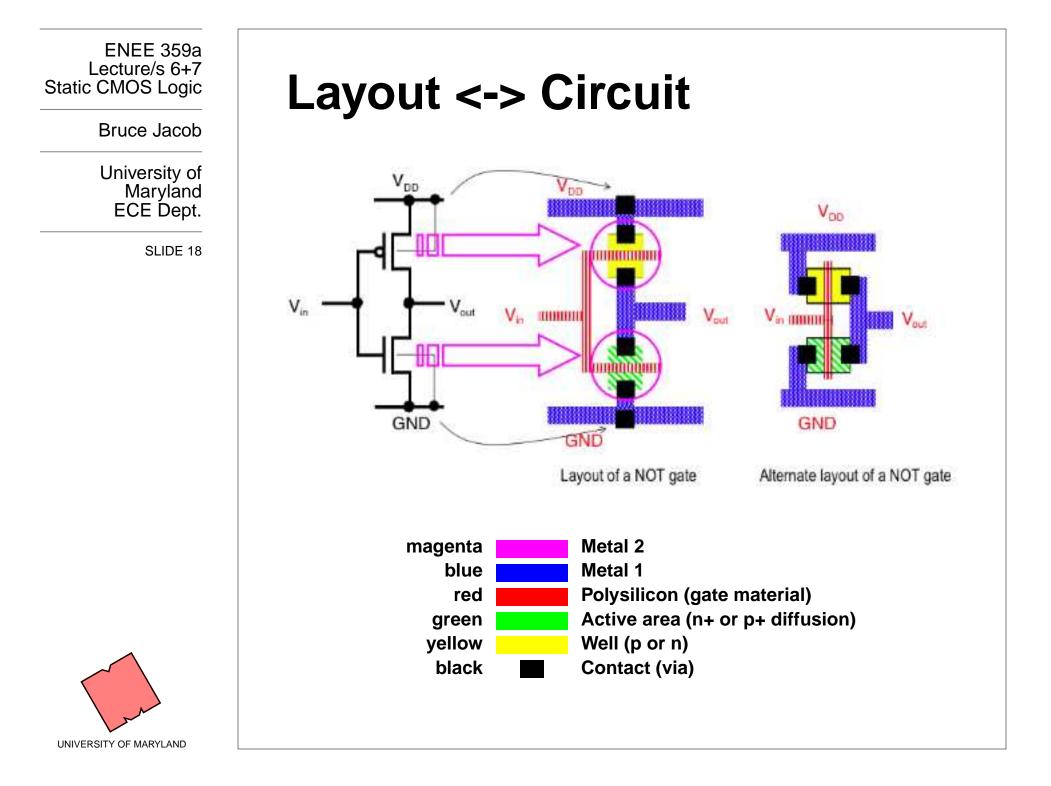

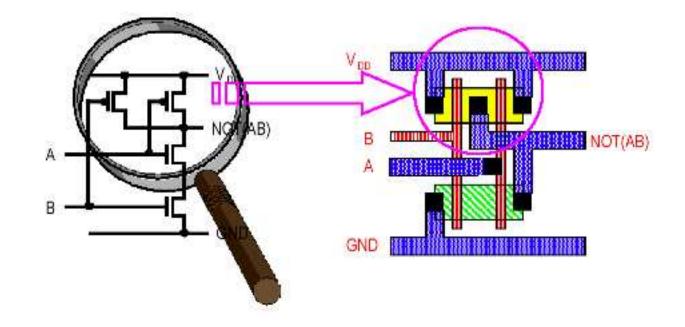

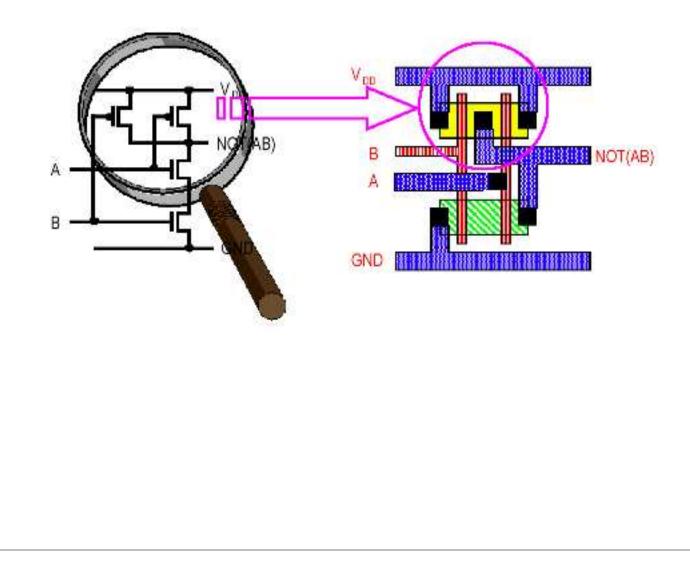

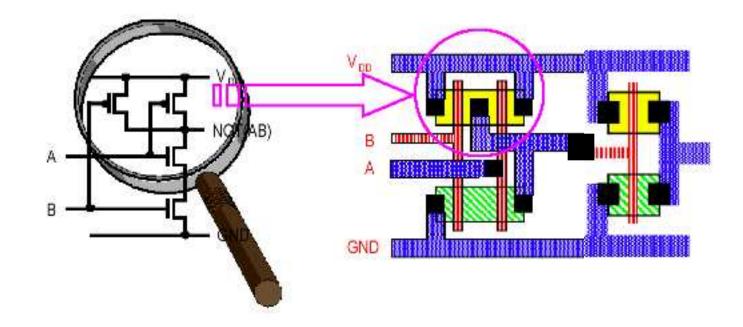

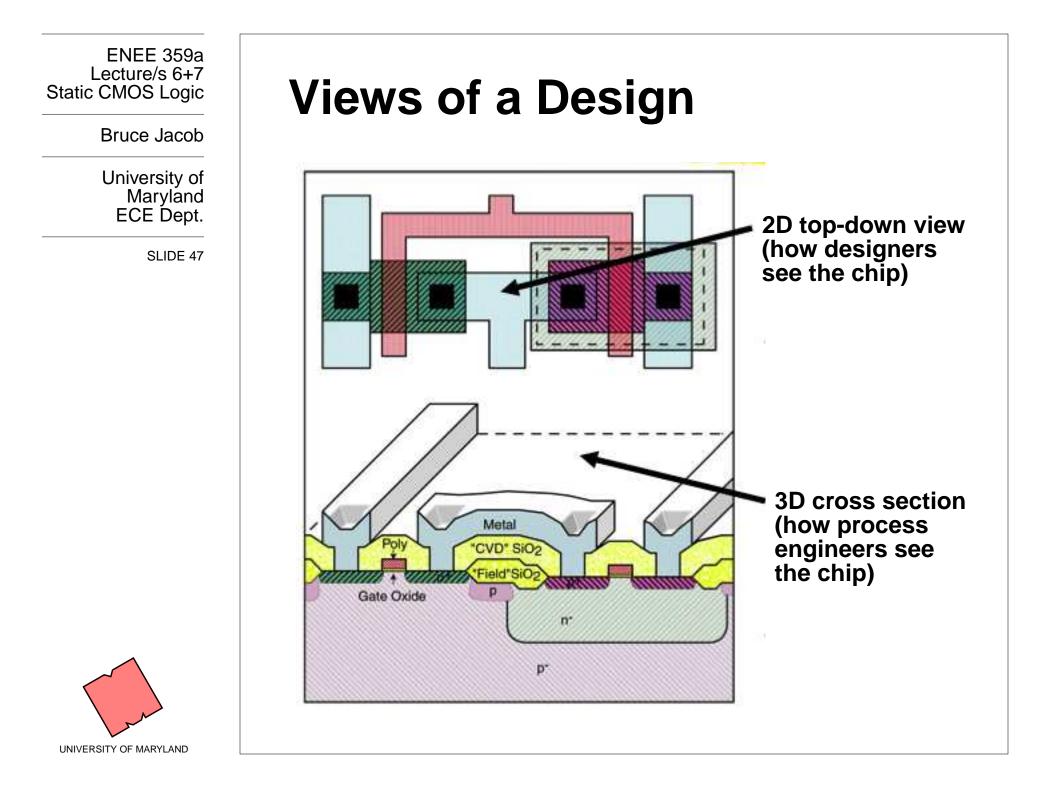

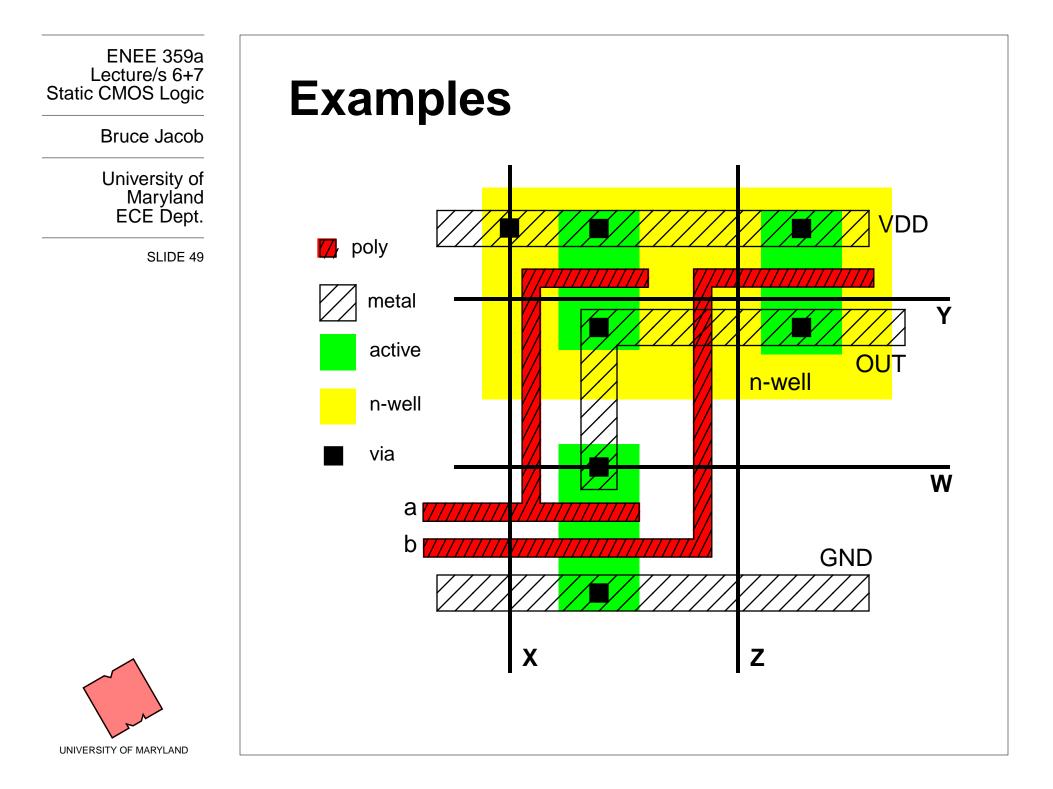

### Layout <-> Circuit

#### **2-INPUT NAND**

- FETs in series (in NAND PDN): source-drain overlap

- FETs in parallel (in NAND PUN): share drain

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 21

### Layout <-> Circuit

#### How About 2-INPUT AND?

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 22

### Layout <-> Circuit

#### How About 2-INPUT AND?

#### Add an inverter at the end ...

Bruce Jacob

University of Maryland ECE Dept.

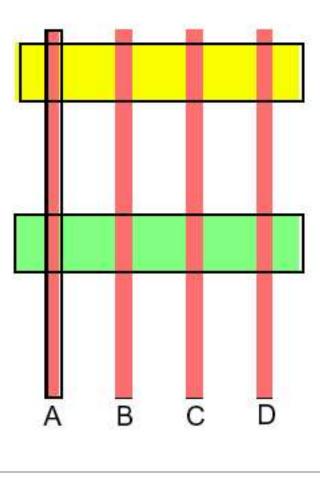

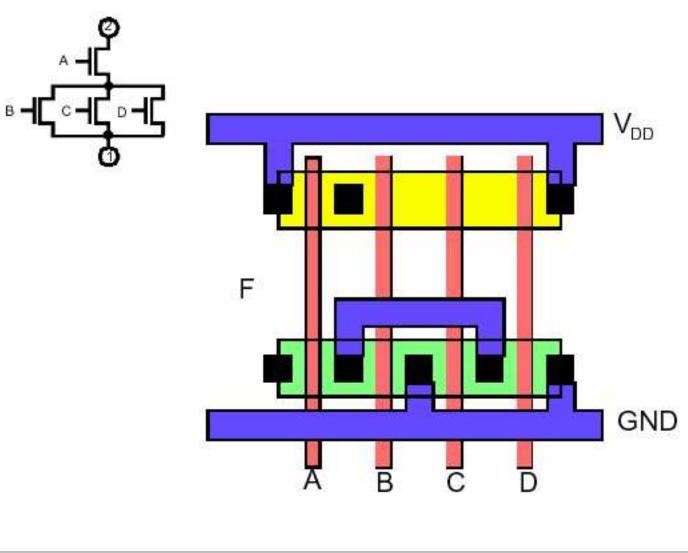

SLIDE 23

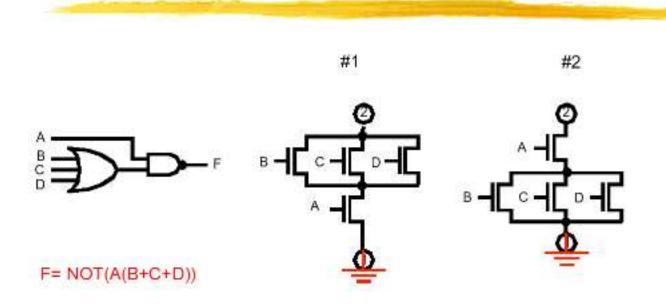

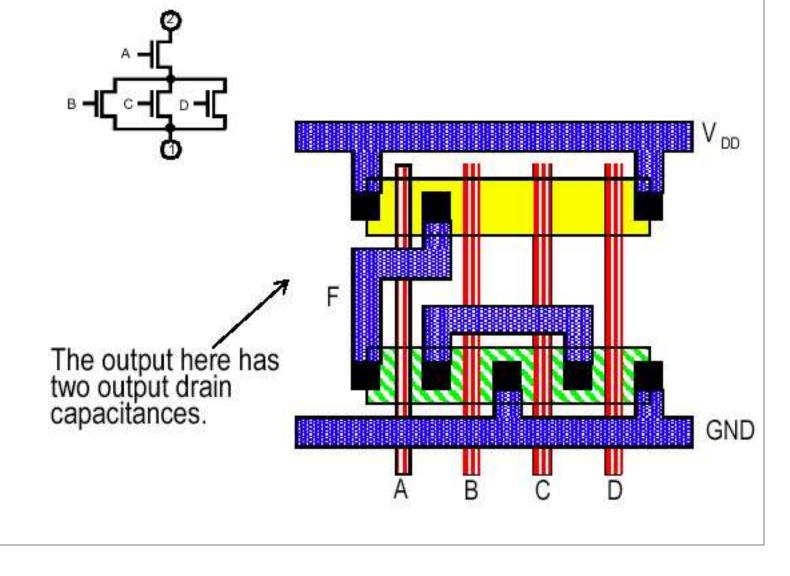

## Examples: Layout <-> Circuit

### NOT ALL LAYOUTS ARE CREATED EQUAL

Complex Logic Gates: OAI Gates

Let's look at two "equivalent" approaches

#### NOT ALL LAYOUTS ARE CREATED EQUAL

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

#### NOT ALL LAYOUTS ARE CREATED EQUAL

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

#### NOT ALL LAYOUTS ARE CREATED EQUAL

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

#### NOT ALL LAYOUTS ARE CREATED EQUAL

Another design of same gate (circuit above simply flipped)

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

#### NOT ALL LAYOUTS ARE CREATED EQUAL

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

#### NOT ALL LAYOUTS ARE CREATED EQUAL

ENEE 359a Lecture/s 6+7

**Bruce Jacob**

University of Maryland ECE Dept.

Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

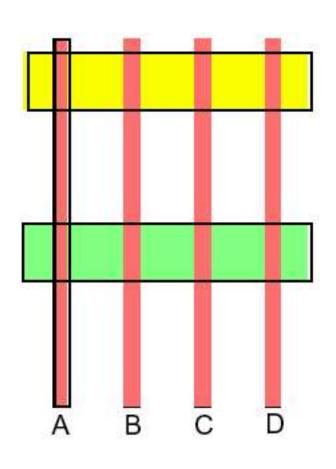

SLIDE 30

# Examples: Layout <-> Circuit

**Gate Design Procedure**

- Run VDD & GND in metal at top & bottom

- Run vertical poly for each gate input

- Order gates to allow maximum source-drain abutting

- Place max # n-diffusions close to GND

- Place max # p-diffusions close to VDD

- Make remaining connections with metal (try to minimize metal usage)

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 31

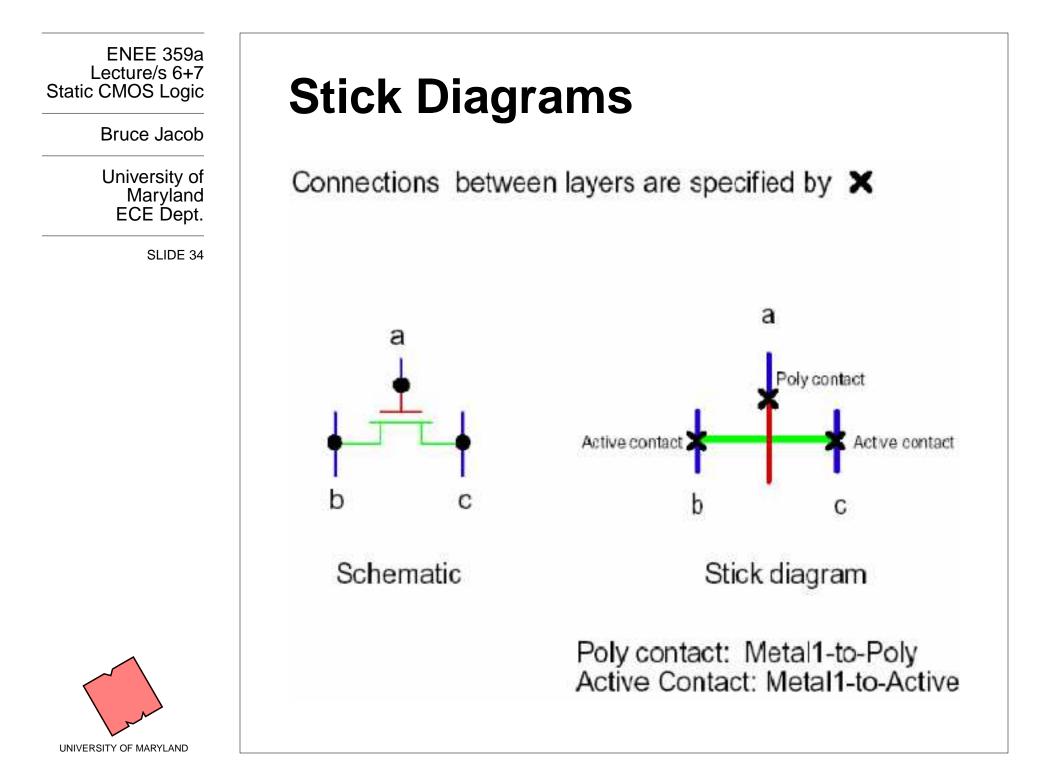

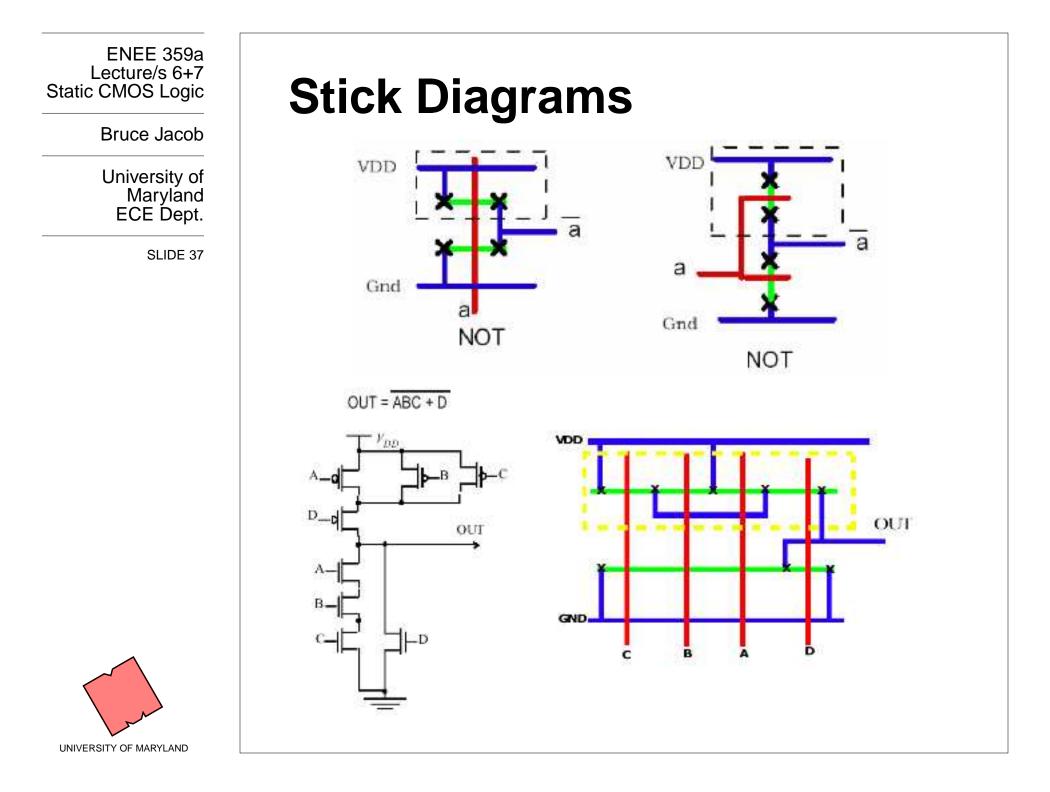

# **Stick Diagrams**

- Introduced by Mead & Conway in 80's

- Every line of conduction-material layer is represented by line of distinct color

Bruce Jacob

University of Maryland ECE Dept.

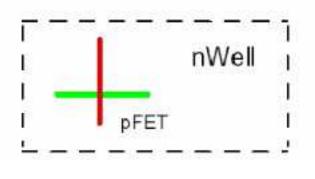

SLIDE 32

# **Stick Diagrams**

In terms of stick diagrams, we thus say that an nFET is formed whenever

Red (Poly) crosses over Green (Active)

DFET

This is consistent with a top view of the transistor.

A pFET is described by the same "red over green" coding, but the crossing point is contained within an nWell boundary

| ENEE 359a         |

|-------------------|

| Lecture/s 6+7     |

| Static CMOS Logic |

Bruce Jacob

University of Maryland ECE Dept.

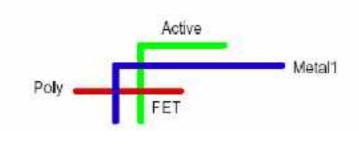

SLIDE 33

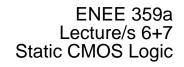

# **Stick Diagrams**

The rules for constructing stick diagrams are based on the characteristics of the conducting layers.

Active

FET

Poly

· Only the routing is important, not the line widths

Blue may cross over green or red without a connection (Active) (Poly)

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 35

# **Stick Diagrams**

Metal lines on different layers can cross one another. Contacting two metal lines requires a via

| ENEE 359a         |

|-------------------|

| Lecture/s 6+7     |

| Static CMOS Logic |

Bruce Jacob

University of Maryland ECE Dept.

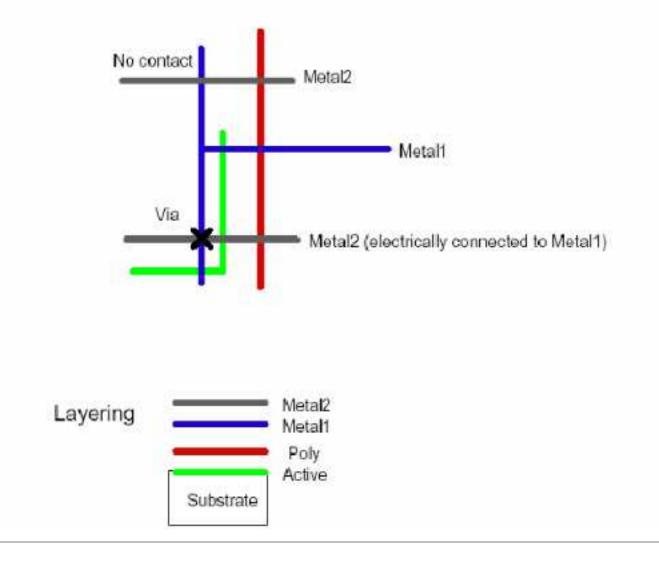

SLIDE 36

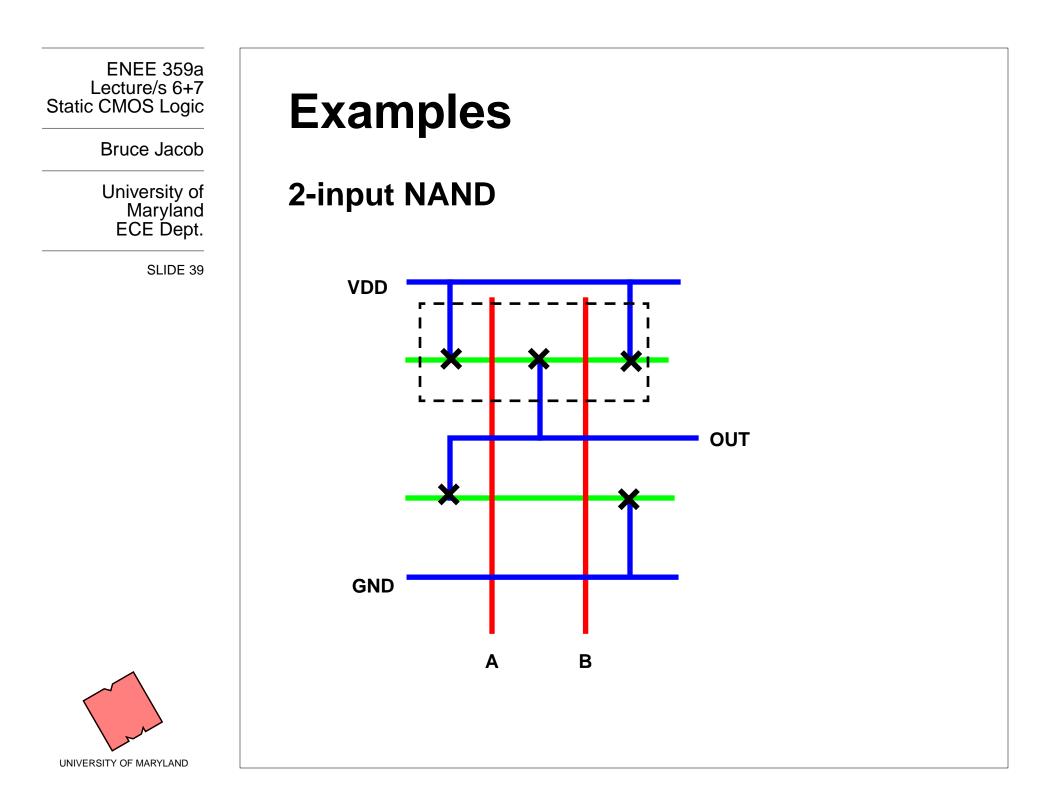

# **Stick Diagrams**

To create CMOS logic gates, we start with the VDD and VSS (ground) lines. We will use a horizontal orientation for the lines. Remember that stick diagrams only deal with the routing. Widths and spacings are not important.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 38

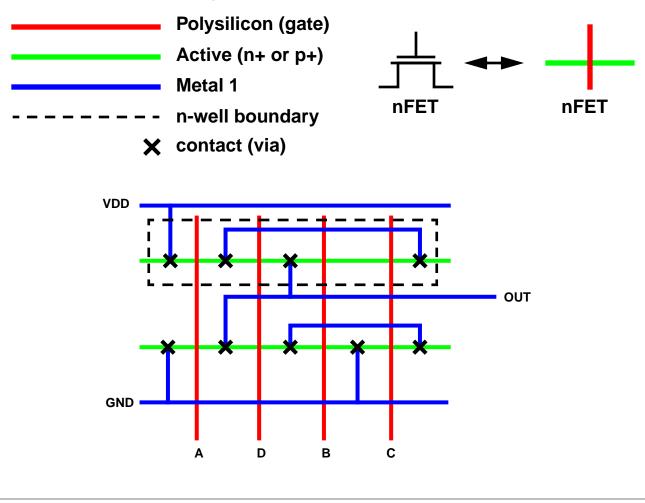

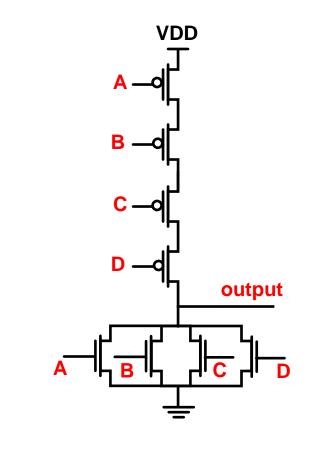

## **Examples**

2-input NAND

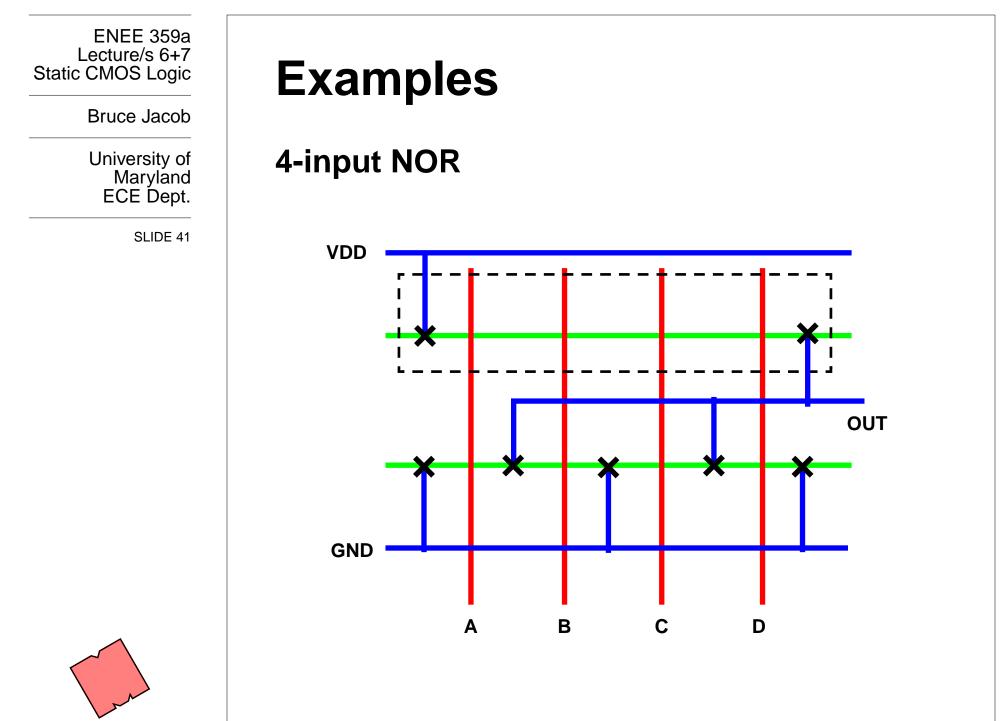

## **Examples**

#### 4-input NOR

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

UNIVERSITY OF MARYLAND

Bruce Jacob

University of Maryland ECE Dept.

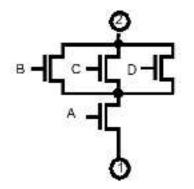

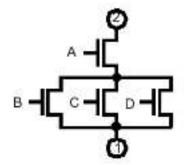

SLIDE 42

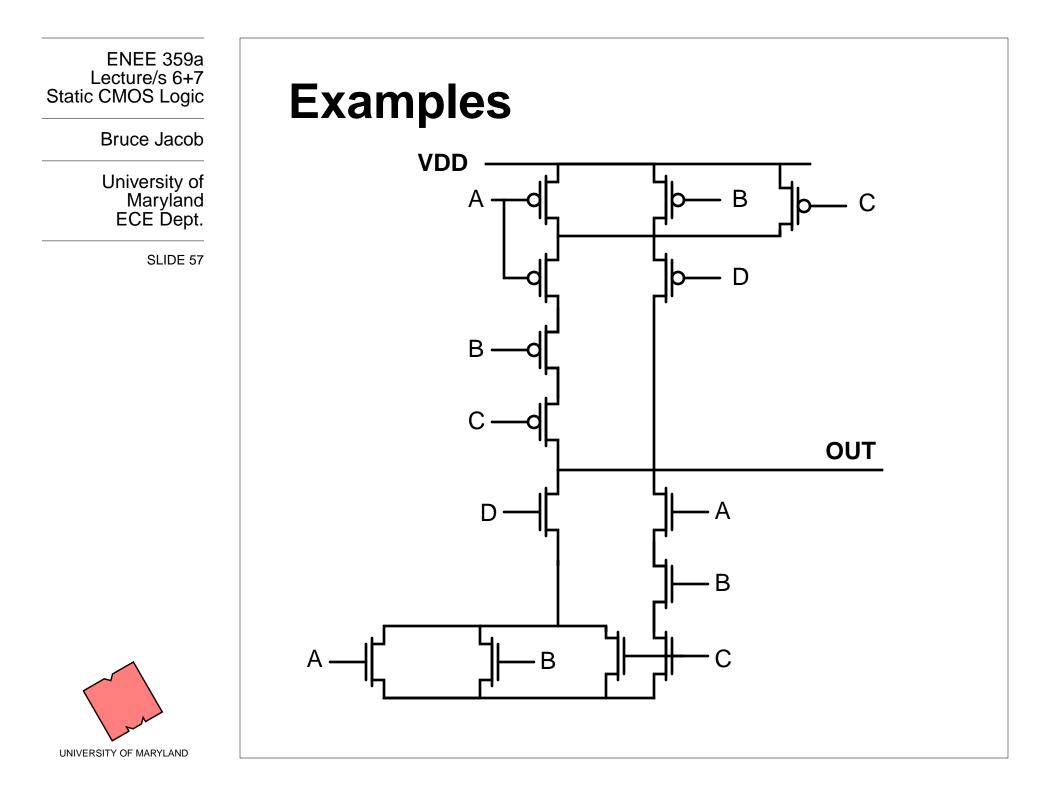

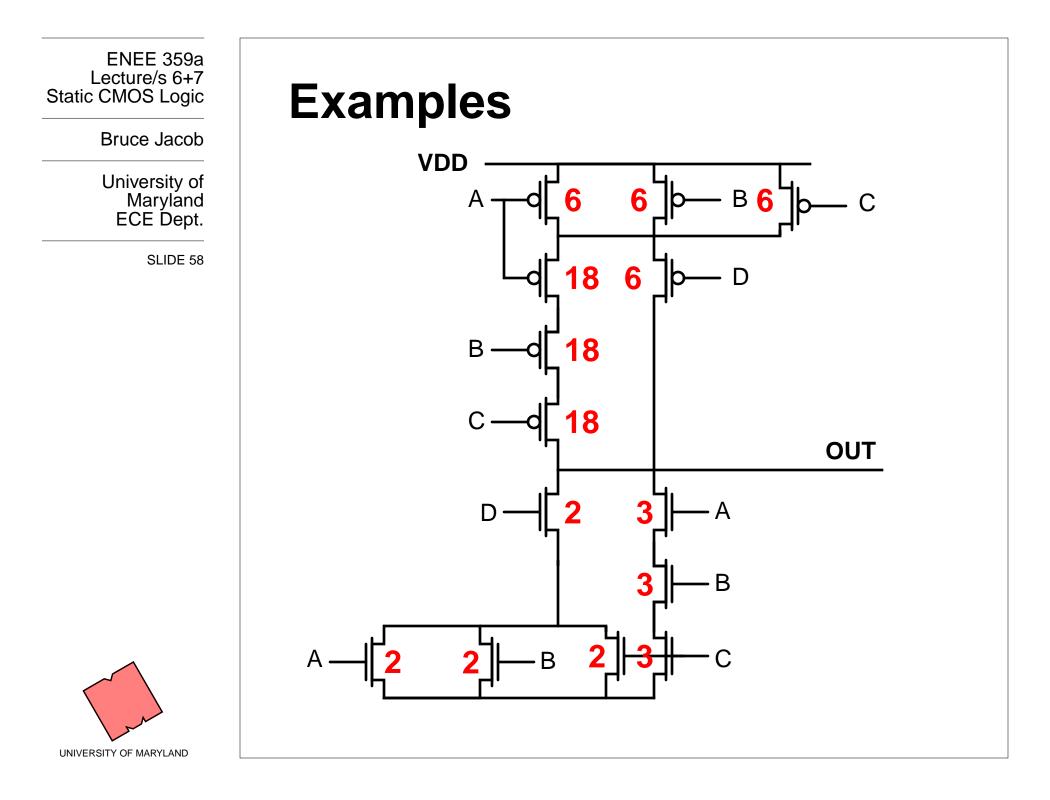

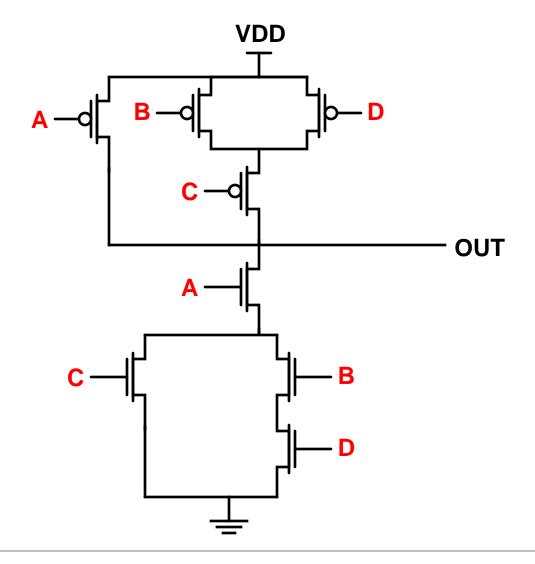

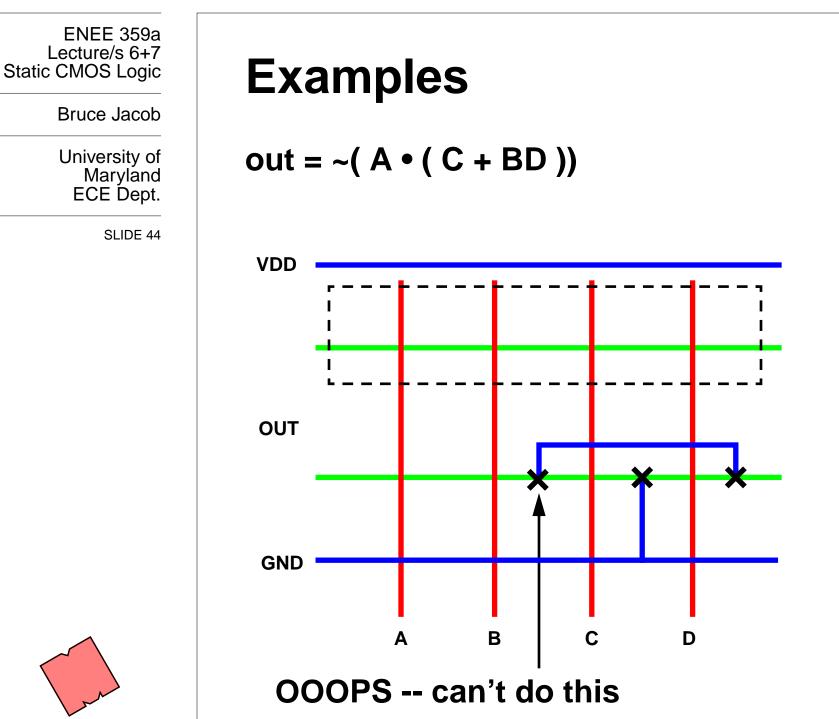

## **Examples**

out = ~( A • ( C + BD ))

## **Examples**

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.

UNIVERSITY OF MARYLAND

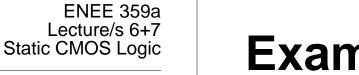

# Examples

VDD OUT GND Α В D С

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 50

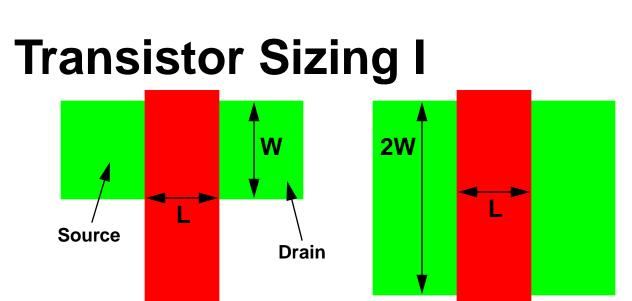

# Sizing: What is a MOSFET?

**A resistor:**

$$\boldsymbol{R}_{n} = \frac{1}{\mu_{n}\boldsymbol{C}_{ox}(\boldsymbol{V}_{GS} - \boldsymbol{V}_{Tn})} \left(\frac{\boldsymbol{L}}{\boldsymbol{W}}\right)$$

(among other things ...) Increasing W decreases the resistance; allows more current to flow

Oxide capacitance  $C_{ox} = \epsilon_{ox}/t_{ox}$  [F/cm<sup>2</sup>] Transconductance  $\beta_n = \mu_n C_{ox} \left(\frac{W}{L}\right) = k'_n \left(\frac{W}{L}\right)$ Gate capacitance  $C_G = C_{ox} WL$  [F]

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 51

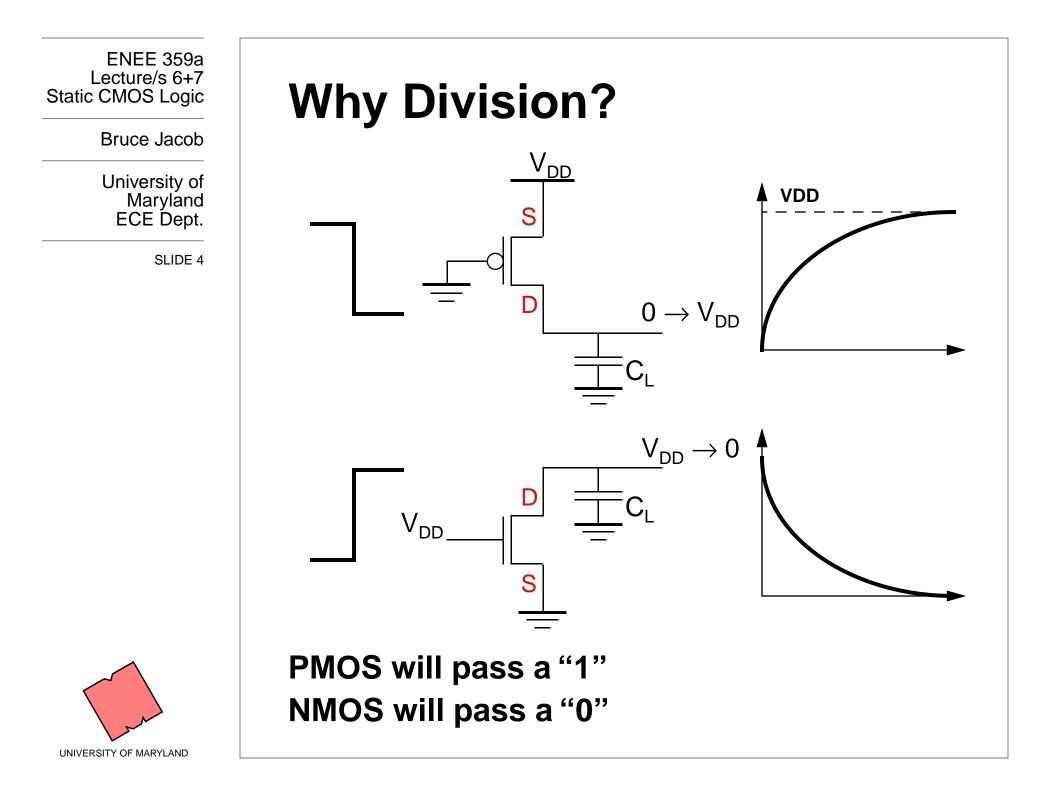

# nFET vs. pFET

$$\boldsymbol{R}_{n} = \frac{1}{\beta_{n}(\boldsymbol{V}_{DD} - \boldsymbol{V}_{Tn})} \qquad \beta_{n} = \mu_{n}\boldsymbol{C}_{ox}\left(\frac{\boldsymbol{W}}{\boldsymbol{L}}\right)_{n}$$

$$\boldsymbol{R}_{p} = \frac{1}{\beta_{p}(\boldsymbol{V}_{DD} - |\boldsymbol{V}_{Tp}|)} \qquad \beta_{p} = \mu_{p}\boldsymbol{C}_{ox}\left(\frac{\boldsymbol{W}}{\boldsymbol{L}}\right)_{p}$$

$$\frac{\mu_n}{\mu_p} = r \quad \begin{array}{l} \text{Typically} \\ \textbf{(2..3)} \end{array}$$

#### (µ is the carrier mobility through device)

# The electrical characteristics of transistors determine the switching speed of a circuit

Need to select the aspect ratios (W/L)<sub>n</sub> and (W/L)<sub>p</sub> of every FET in the circuit

#### Define Unit Transistor (R<sub>1</sub>, C<sub>1</sub>)

- L/W<sub>min</sub>-> highest resistance (needs scaling)

- $R_2 = R_1 \div 2 \text{ and } C_2 = 2 \bullet C_1$

- Separate nFET and pFET unit transistors

- Unit devices are *not* restricted to individual transistors

ENEE 359a Lecture/s 6+7 Static CMOS Logic

Bruce Jacob

University of Maryland ECE Dept.