Dave Wang

University of Maryland ECE Dept.

SLIDE 1

### ENEE 302H, Fall 2004 Digital Electronics

### **Manufacturing**

### David Wang davewang@eng.umd.edu

Credit where credit is due:

Slides contain original artwork (© Wang 2004) as well as material taken liberally from AMD and Intel. The respective copyrights remain with AMD and Intel, respectively.

Dave Wang

University of Maryland ECE Dept.

SLIDE 2

## **Overview**

- What makes silicon a good base to build on? Why not other stuff? (Discussion: the Silicon CMOS Steamroller)

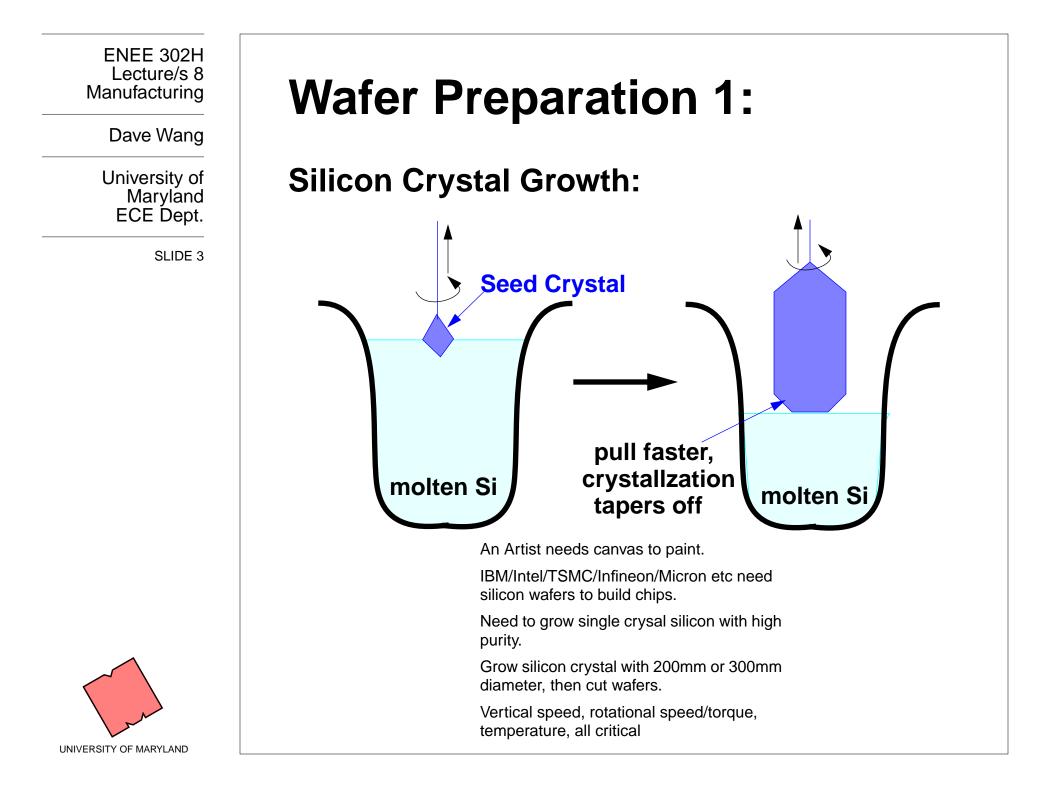

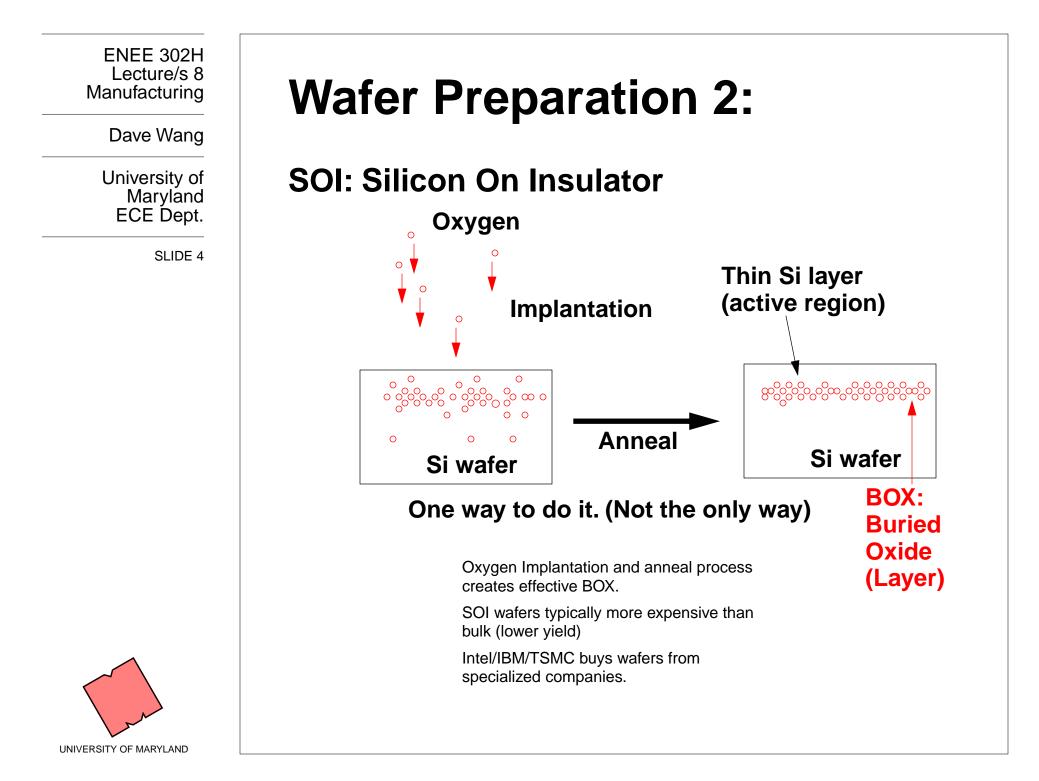

- Wafer preparation. (Bulk, SOI)

- Microelectronics Magic

- Testing

- Packaging

- End Product + Show and Tell.

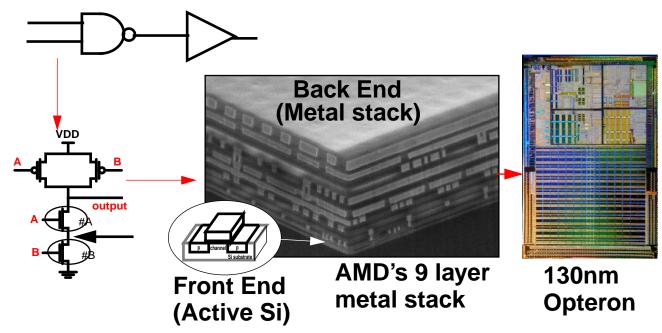

# **Microelectronics Magic 1:**

- Take logic design,

- Translate to circuit design

- Build transistors on active silicon

- Connect transistors

- Get silicon chip: CPU, DRAM, SRAM, Flash, DSP, bio/ chem sensors, communications....

ENEE 302H Lecture/s 8

**Dave Wang**

University of Maryland ECE Dept.

SLIDE 5

Manufacturing

Dave Wang

University of Maryland ECE Dept.

SLIDE 6

## **Microelectronics Magic 2:**

### **Building Layers**

Fundamentally 3D structures

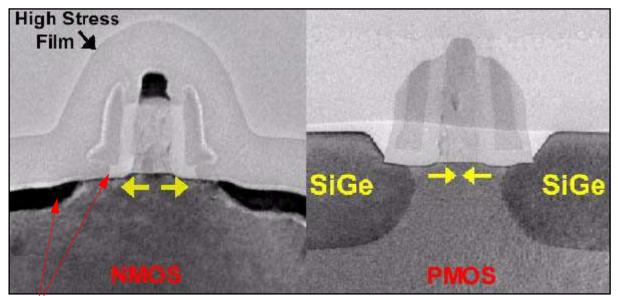

#### Intel's strained-Si @ 90nm

Bottom line: build layers of stuff by adding material or removing material from surface of silicon.

Parallel (Masks and resists, wafer level) or Serial (beams, one line at a time: Ion Beam)

Higher throughput == Lower cost

Material scientists bring new materials into play every generation: Moore's law.

# Microelectronics Magic 3:

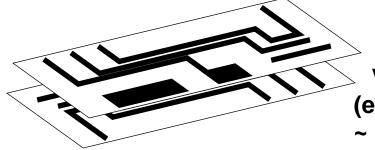

Mask Set

Very expensive

(especially front end)

~ \$1M @ 90nm node\*

#### **Discussion:**

What is a "class 1 fab"?

What is a "stepping"?

Patterning: creating 3D structures Future: MEMS?

Adding (converting) material

Spin on Deposition: CVD Implantation Oxidation **Removing material**

Etching Polishing: CMP Chemically

CVD: Chemical Vapor Deposition CMP: Chemical-Mechanical Polishing \*Estimate given by IC Knowledge LLC

ENEE 302H Lecture/s 8 Manufacturing

Dave Wang

University of Maryland ECE Dept.

SLIDE 7

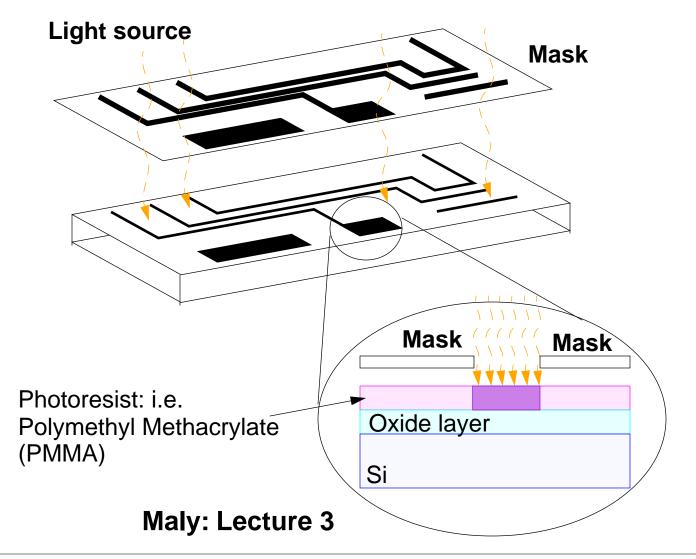

## **Microelectronics Magic 4:**

#### Lithography

ENEE 302H Lecture/s 8 Manufacturing

Dave Wang

University of Maryland ECE Dept.

SLIDE 8

Dave Wang

University of Maryland ECE Dept.

SLIDE 9

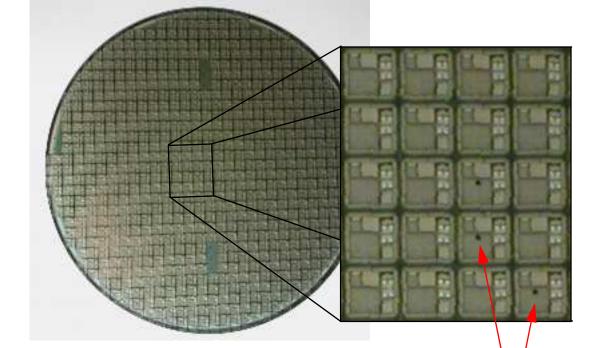

You've made it. Does it work?

Millions of transistors, 100% functional? If not, how do you find the failed one?

Functional Tests Wafer probe Defective IDDQ Infrared BIST

#### Dave Wang

University of Maryland ECE Dept.

SLIDE 10

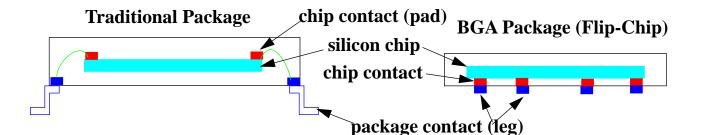

# Packaging:

#### **Connecting chips to each other**