Bruce Jacob

University of Maryland ECE Dept.

SLIDE 1

### ENEE 359a Digital VLSI Design

### **Sequential Logic**

### Prof. Bruce Jacob blj@eng.umd.edu

Credit where credit is due:

Slides contain original artwork (© Jacob 2004) as well as material taken liberally from Irwin & Vijay's CSE477 slides (PSU), Schmit & Strojwas's 18-322 slides (CMU), Dally's EE273 slides (Stanford), Wolf's slides for *Modern VLSI Design*, and/or Rabaey's slides (UCB).

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 2

### **Overview**

- Transmission gates

- Basic storage-cell concepts

- Metastability

- Static latches & registers, brief primer on dynamic logic, dynamic latches & registers, trading off complexity in individual memory elements vs. complexity in clock-delivery network

- Pipelining

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 3

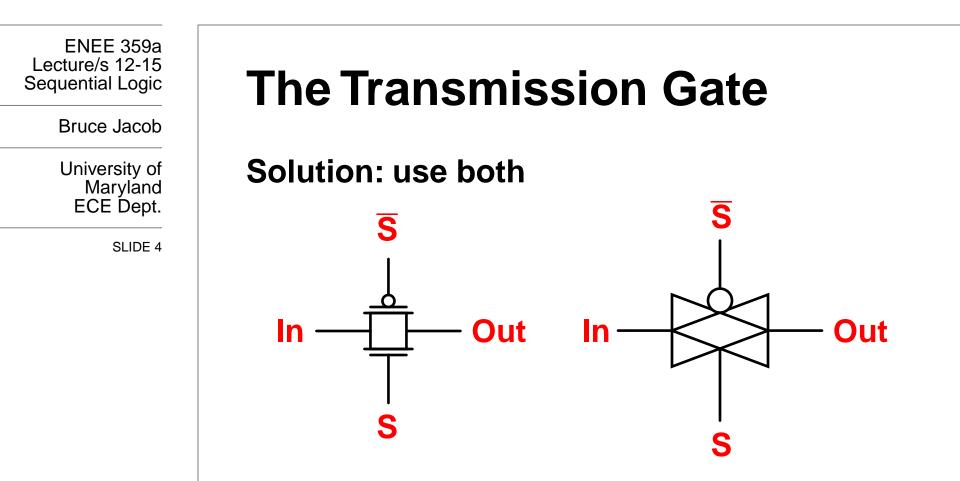

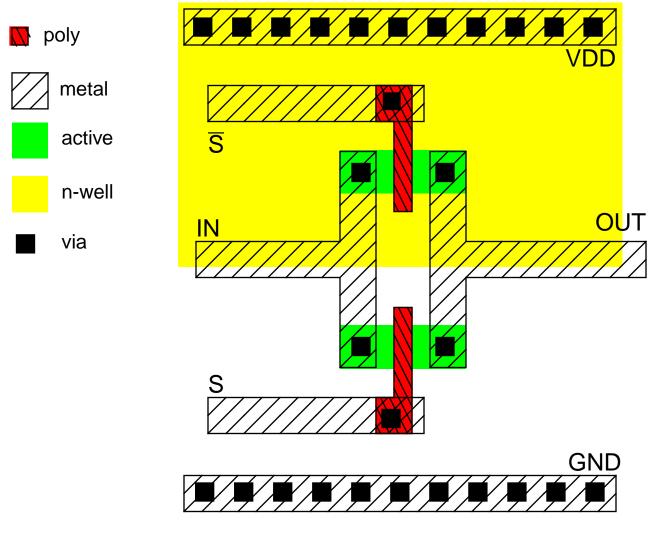

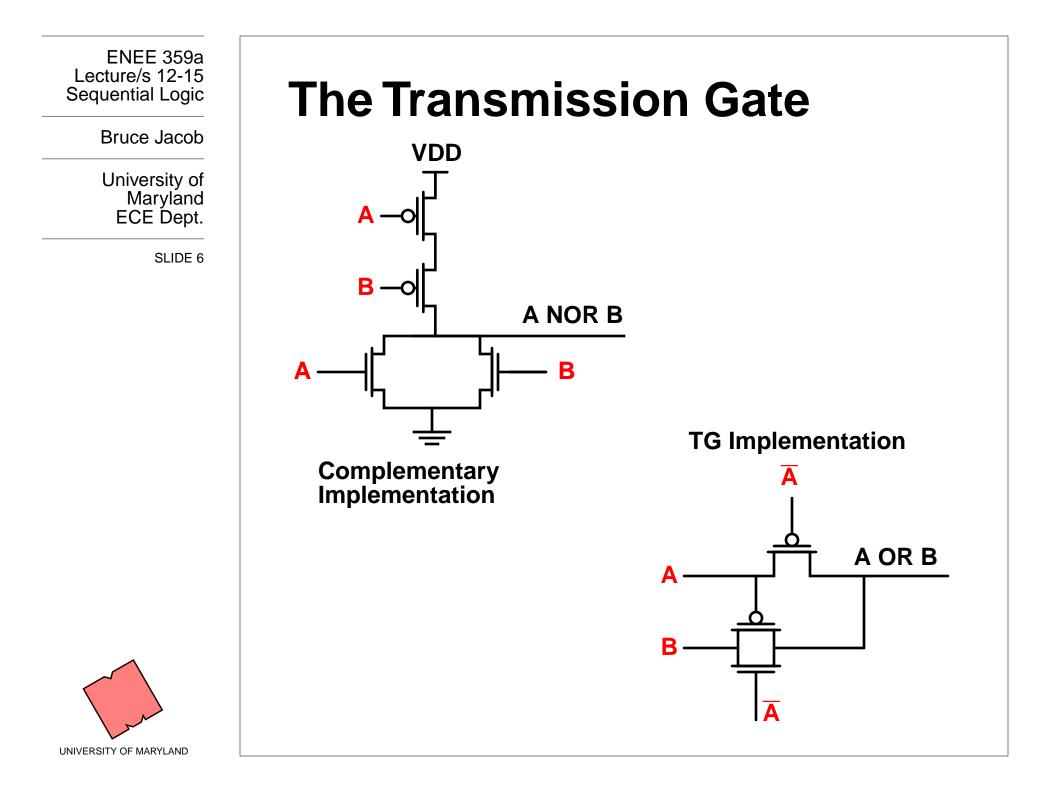

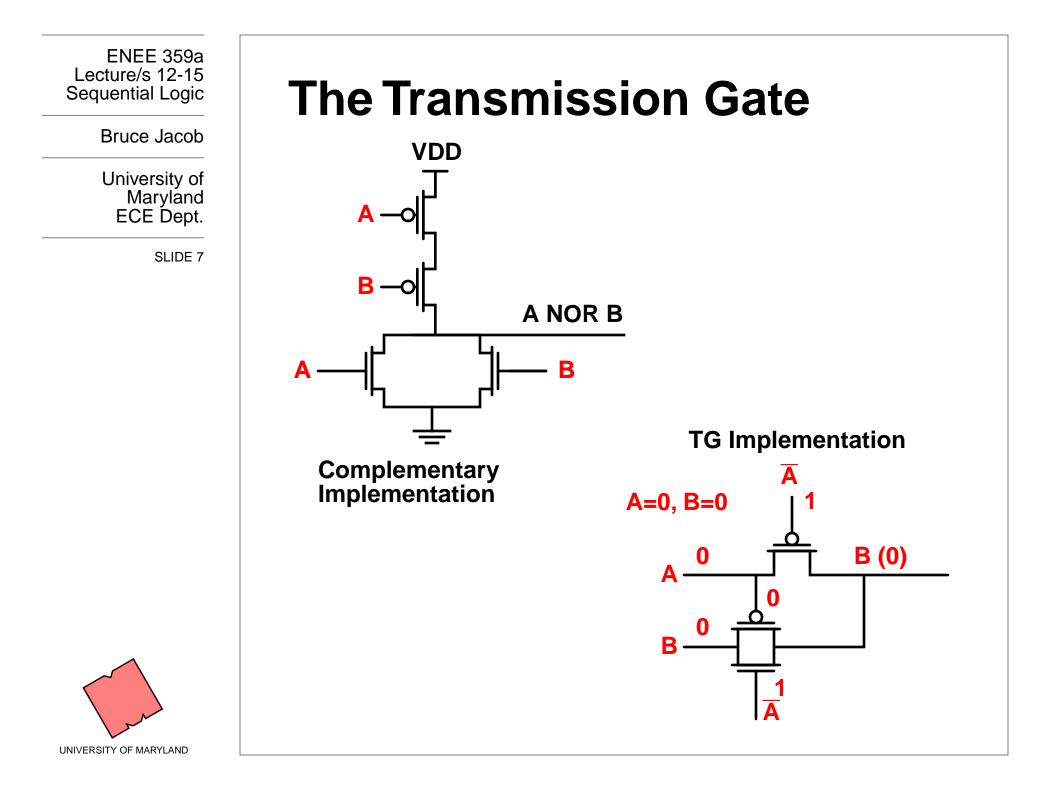

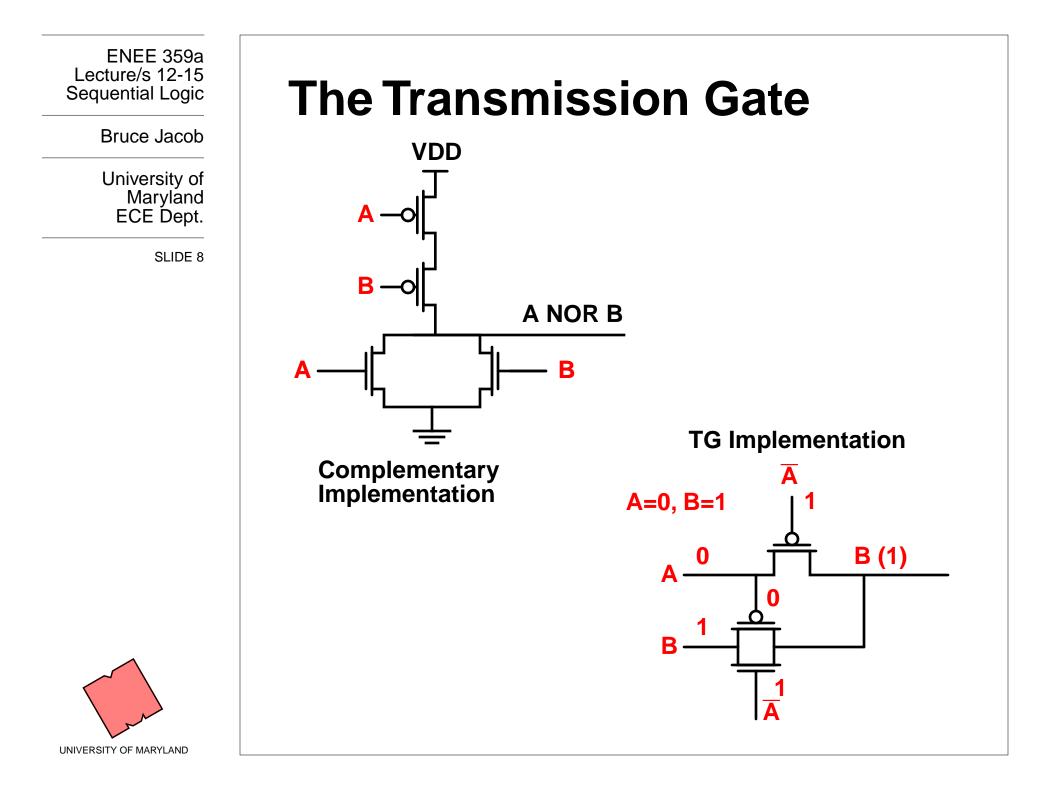

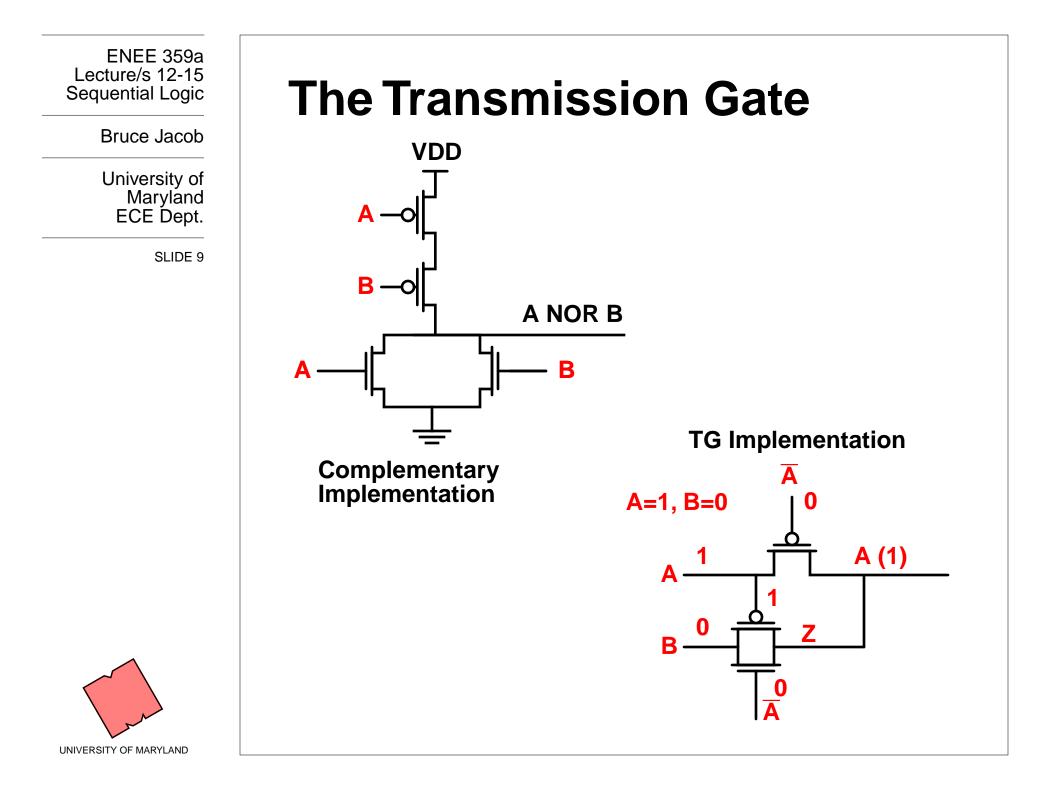

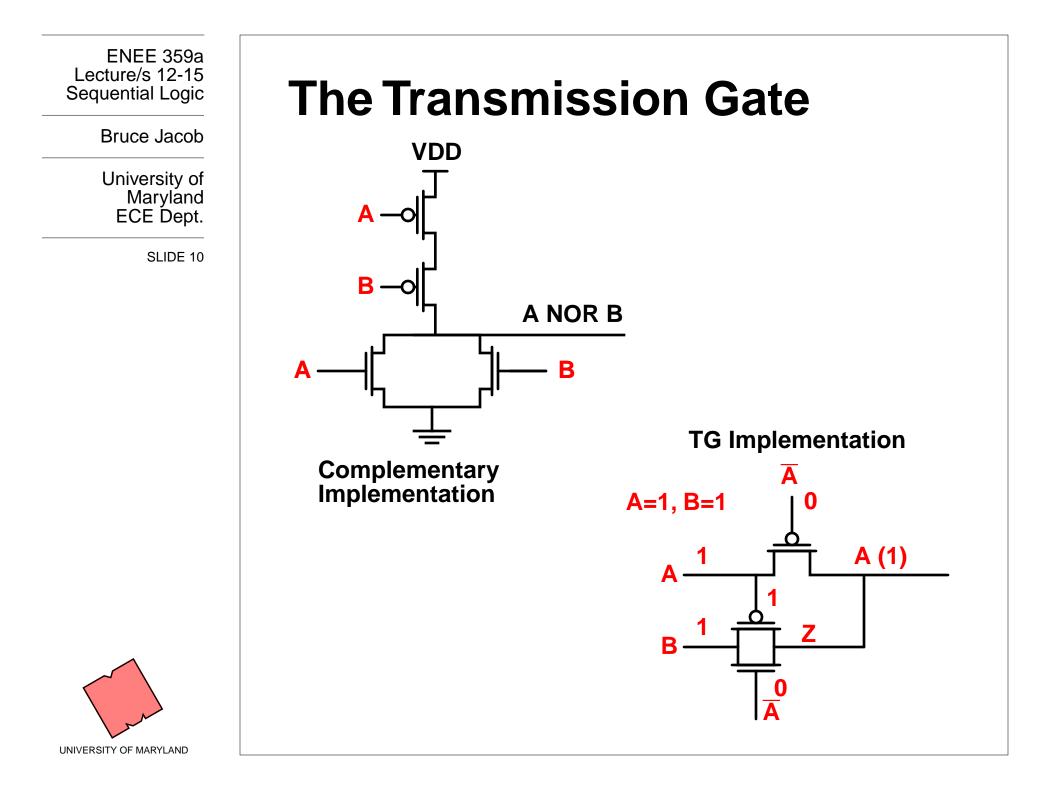

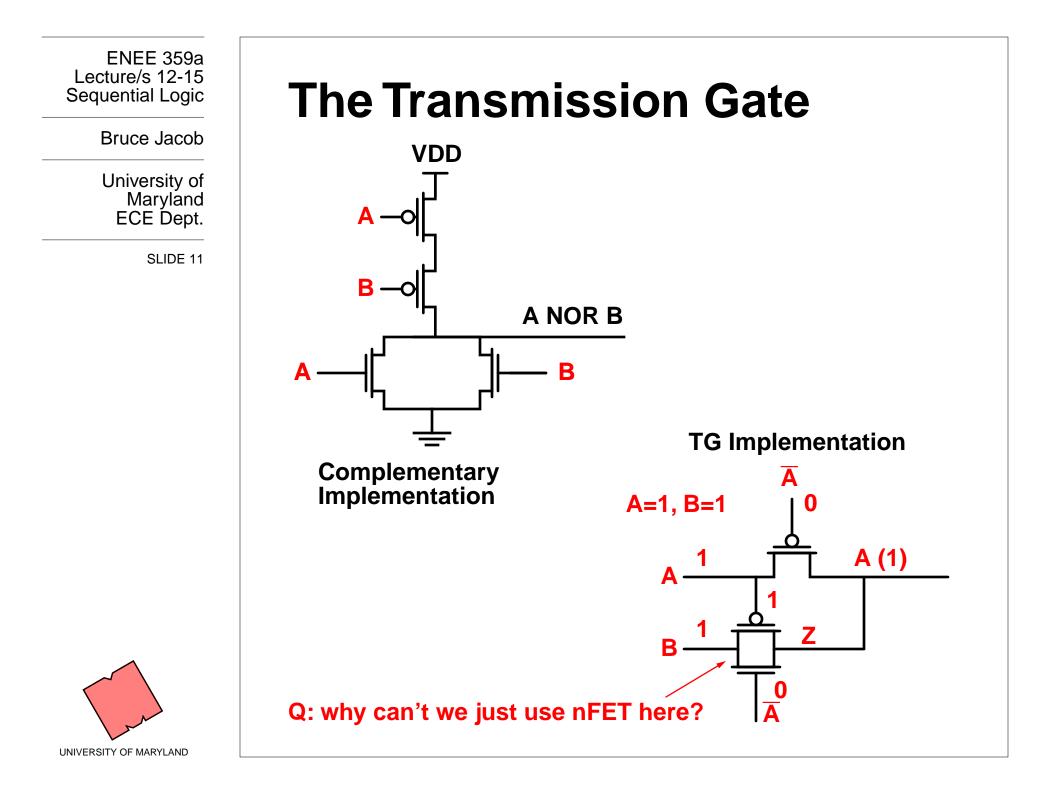

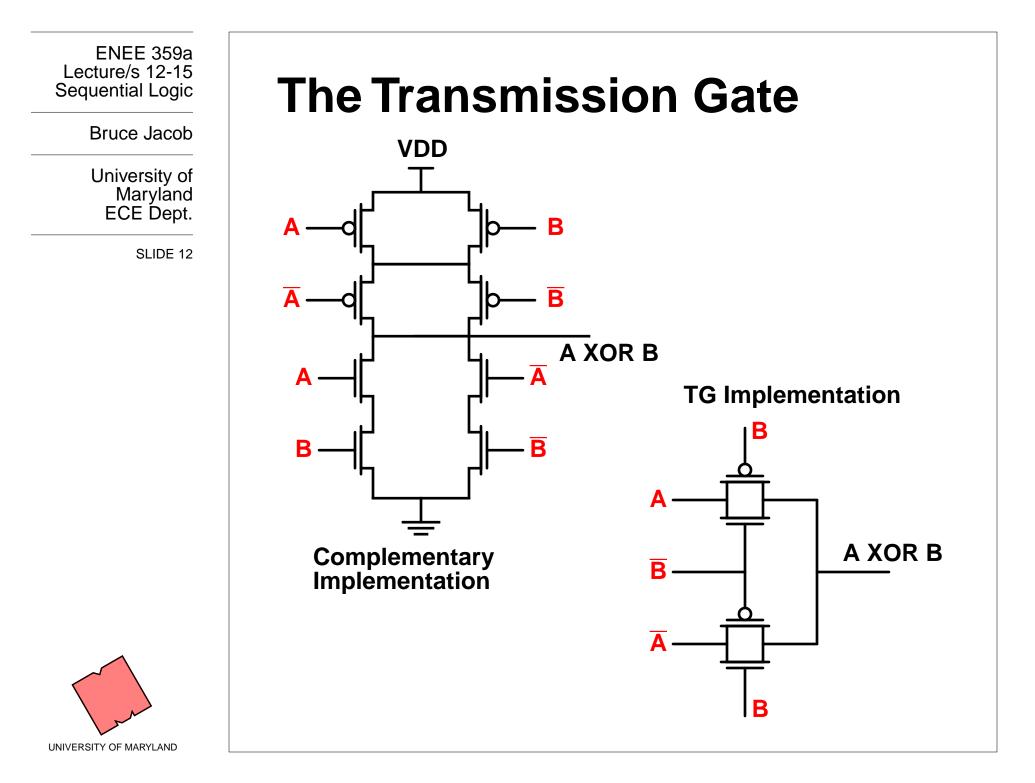

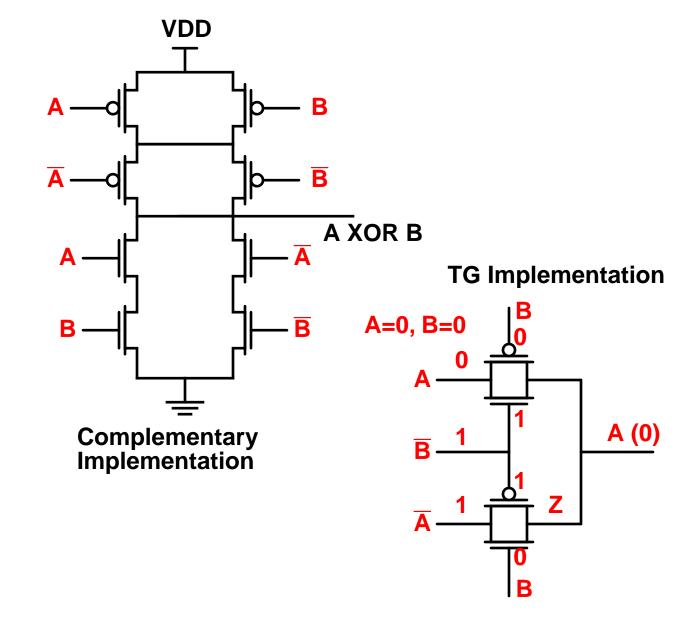

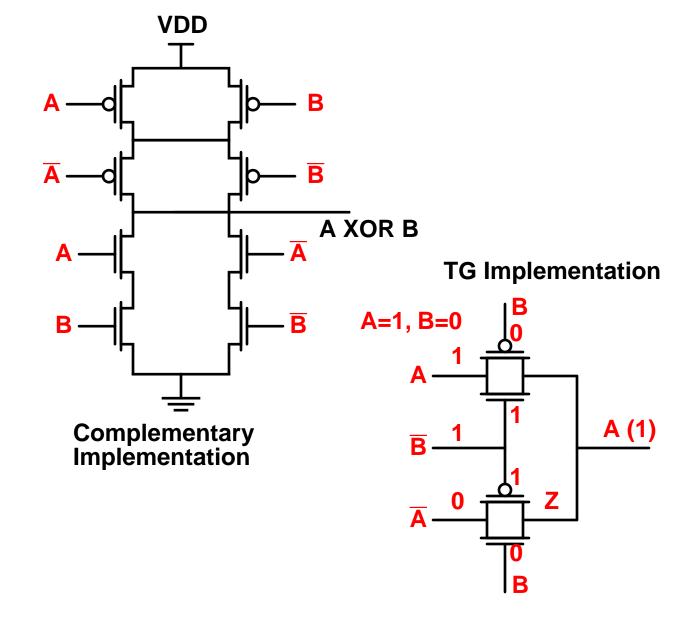

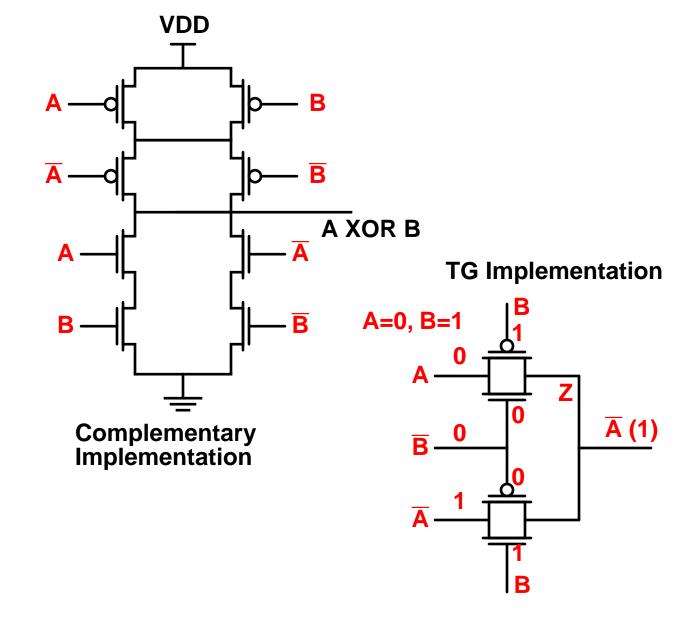

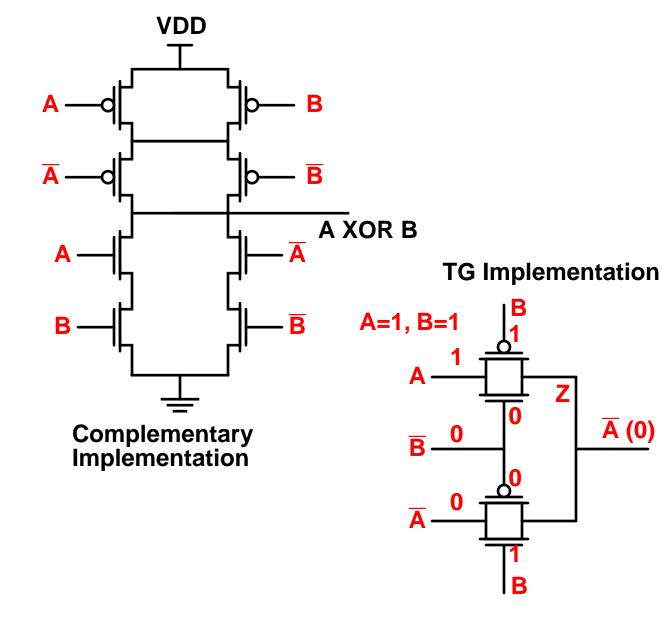

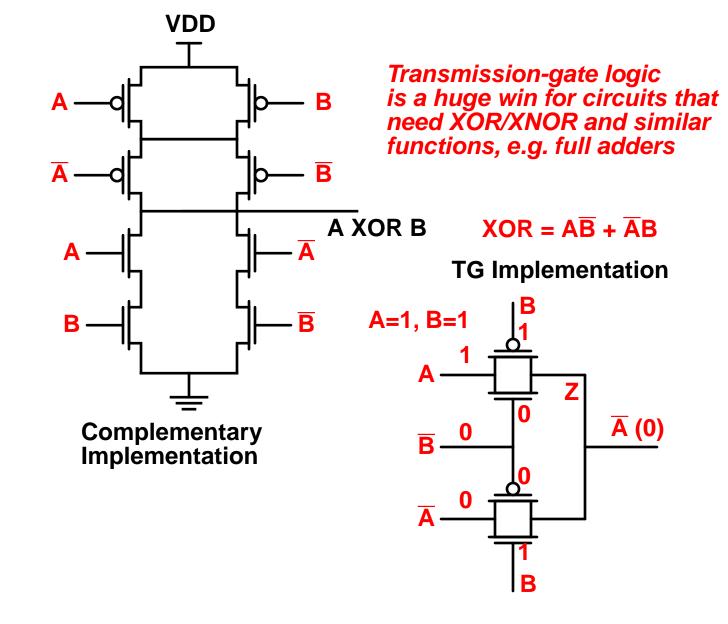

## **The Transmission Gate**

Basic idea: reduce number of transistors in design by allowing inputs to drive not only *gate* terminals but also *source/drain* terminals. (similar in this regard to *pass-transistor* logic)

### Recall:

•

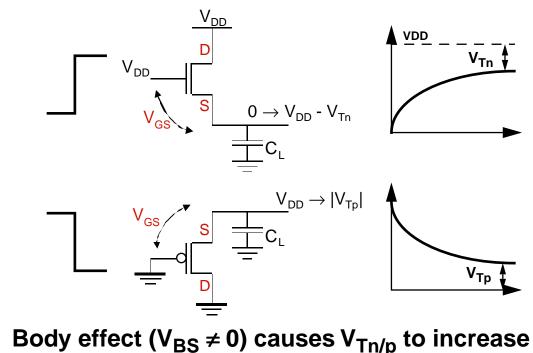

- NMOS will not pass a "1"

- PMOS will not pass a "0"

Out = (S) ? In : Z;

Potential problem: unlike other static logic gates, this can allow output to be *floating* (not connected — thus, easily perturbed by nearby signals such as metal wires above)

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 5

Sometimes standard cell includes S inverter

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 18

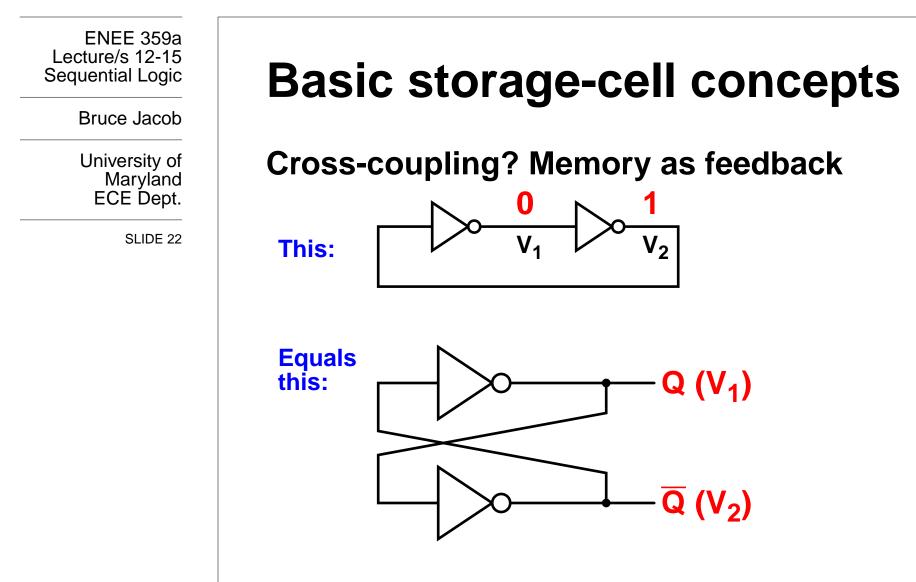

### **Basic storage-cell concepts**

**DEFINITIONS (from the book):**

- 1. Flip-flop: bistable component built by cross-coupling logic gates

- 2. Latch: *level-sensistive* storage element

- 3. Register: edge-triggered storage element

(the literature on the topic is not consistent in its use of these terms, so <u>beware</u> and try to figure out from context what someone means ...)

### **Basic storage-cell concepts**

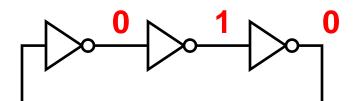

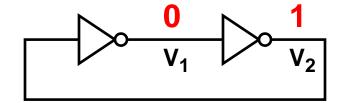

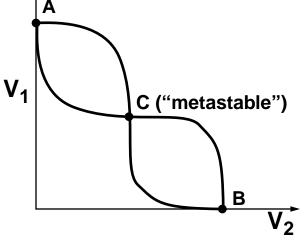

**Bistable? Only two stable points on VTC**

... what happens next?

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

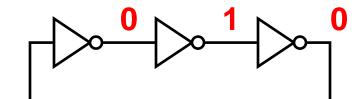

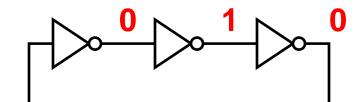

### **Basic storage-cell concepts**

### **Bistable? Only two stable points on VTC**

... what happens next?

... what happens next?

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

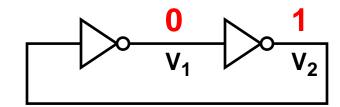

### **Basic storage-cell concepts**

**Bistable? Only two stable points on VTC**

... what happens next?

*this* is a stable circuit (and, in particular, bistable)

UNIVERSITY OF MARYLAND

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

### Question: how do we write a new value?

- Cutting feedback loop (multiplexer-based)

- Overpowering feedback loop

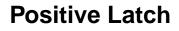

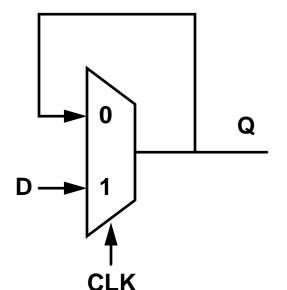

# **Multiplexer-Based Latches**

Negative Latch

ENEE 359a Lecture/s 12-15 Sequential Logic

Bruce Jacob

University of Maryland ECE Dept.

#### ENEE 359a Lecture/s 12-15 Sequential Logic Bruce Jacob University of Maryland ECE Dept.

# Metastability

Bruce Jacob

Sequential Logic

ENEE 359a Lecture/s 12-15

> University of Maryland ECE Dept.

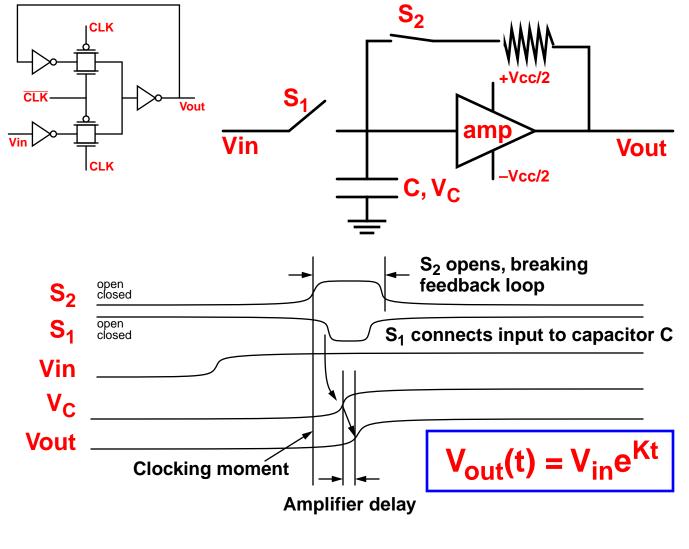

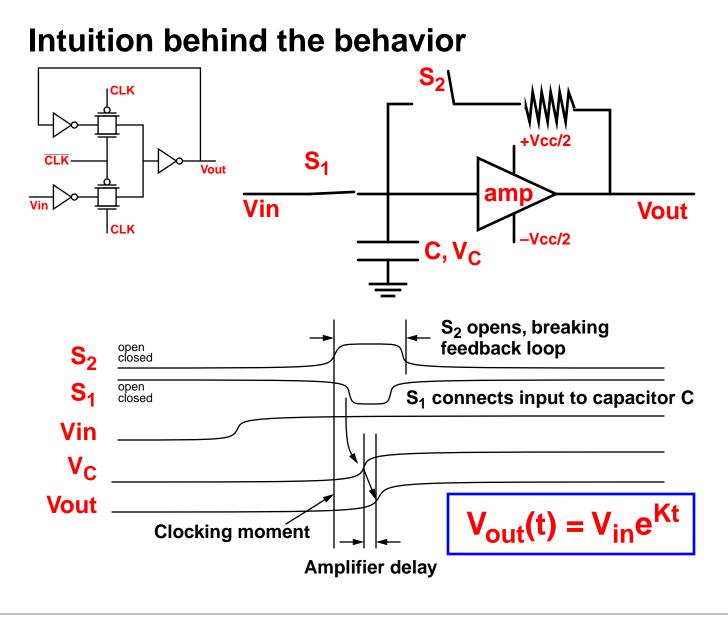

# Metastability

Bruce Jacob

Sequential Logic

ENEE 359a Lecture/s 12-15

> University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 29

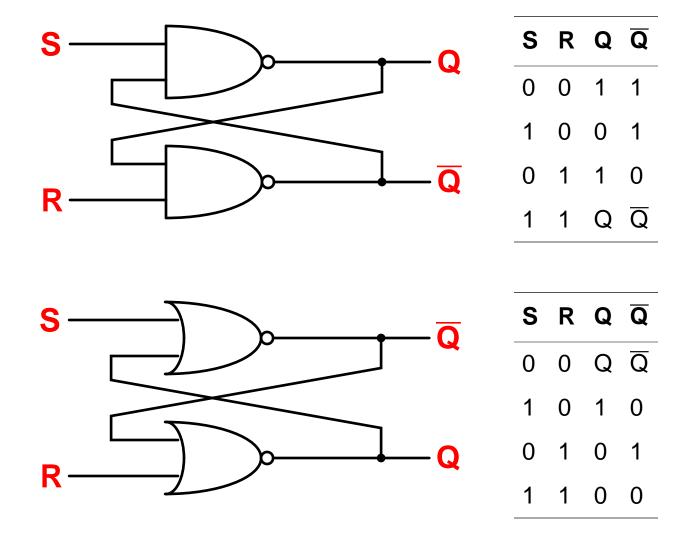

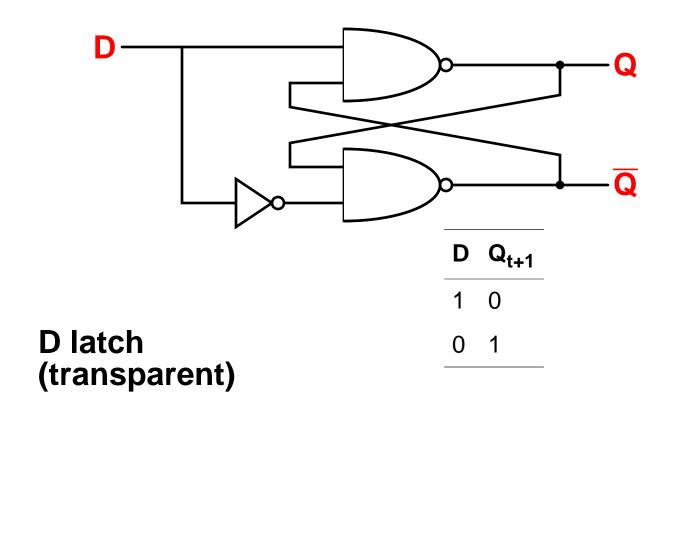

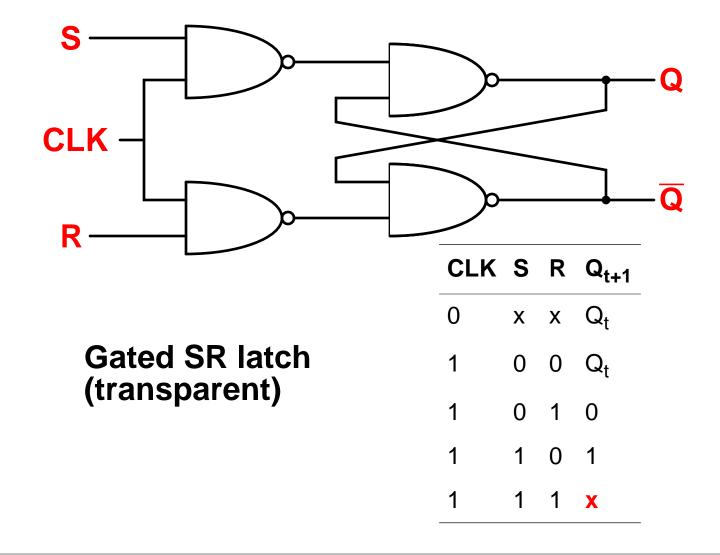

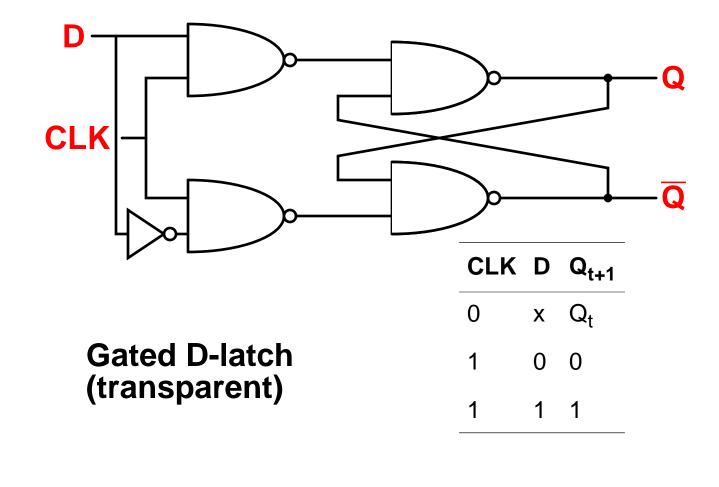

### **Static latches & registers**

Set-Reset Flip-Flop (two types)

Bruce Jacob

University of Maryland ECE Dept.

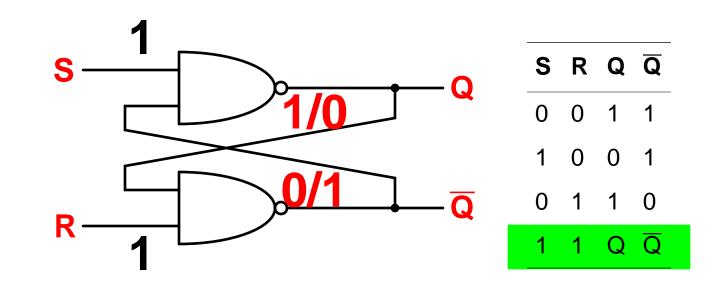

SLIDE 30

## Static latches & registers

**NAND-based SR Flip-Flop**

"forbidden" state,  $Q == \overline{Q}$

Bruce Jacob

University of Maryland ECE Dept.

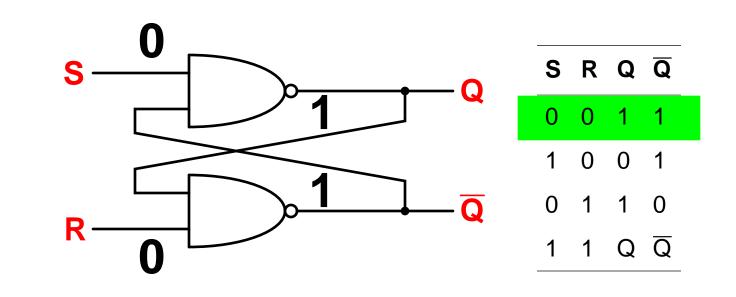

SLIDE 31

## **Static latches & registers**

**NAND-based SR Flip-Flop**

Bruce Jacob

University of Maryland ECE Dept.

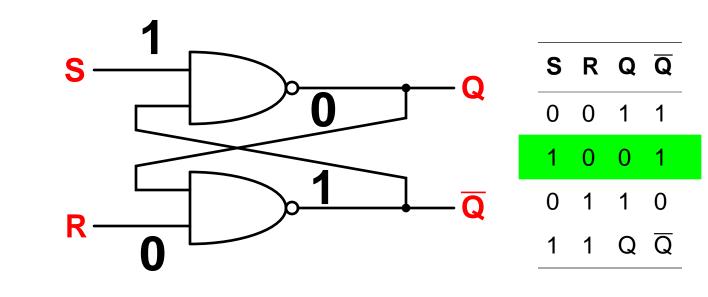

SLIDE 32

## **Static latches & registers**

**NAND-based SR Flip-Flop**

Bruce Jacob

University of Maryland ECE Dept.

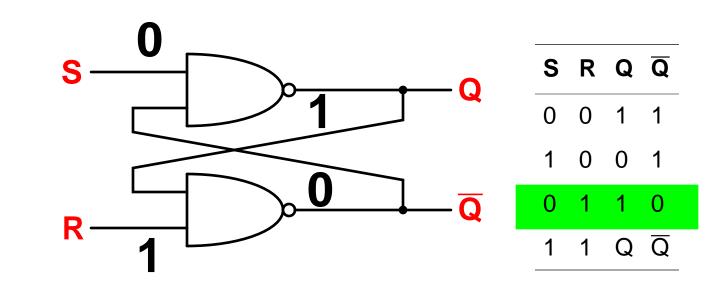

SLIDE 33

## Static latches & registers

**NAND-based SR Flip-Flop**

Q and  $\overline{Q}$  keep their previous values if this state is reached from a non-forbidden state

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 34

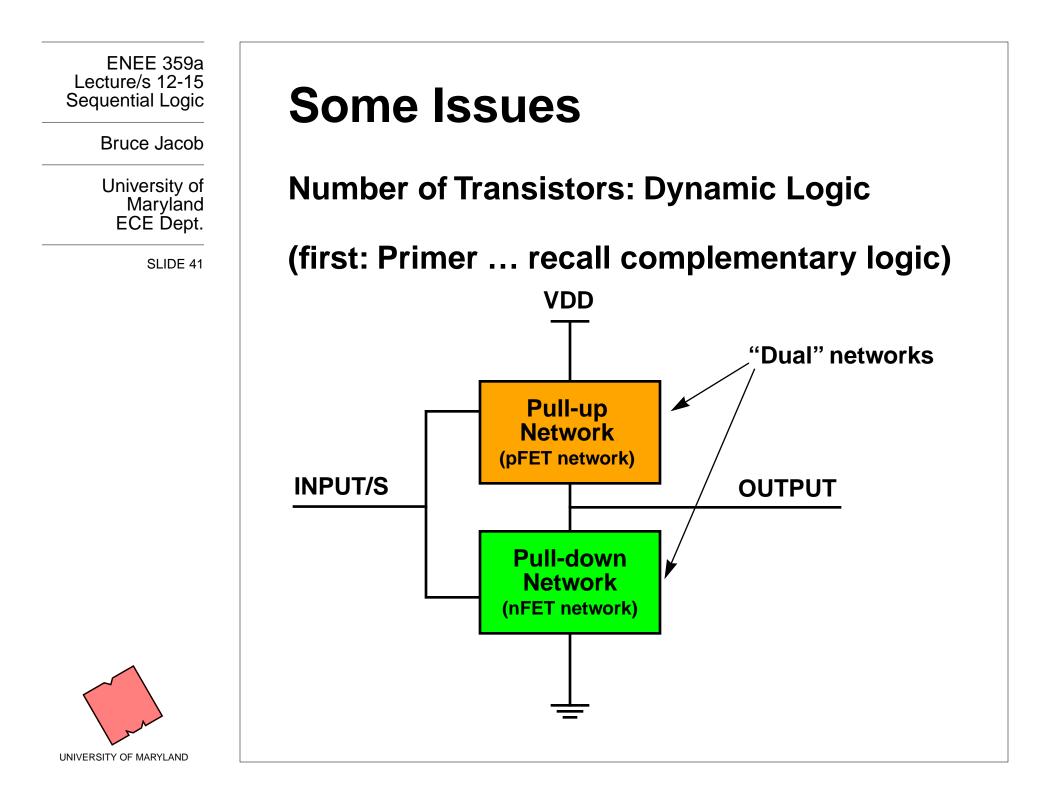

### **Some Issues**

### **Forbidden FF states**

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 35

### **Some Issues**

### **Forbidden FF states**

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 36

### **Some Issues**

### **Forbidden FF states**

Bruce Jacob

University of Maryland ECE Dept.

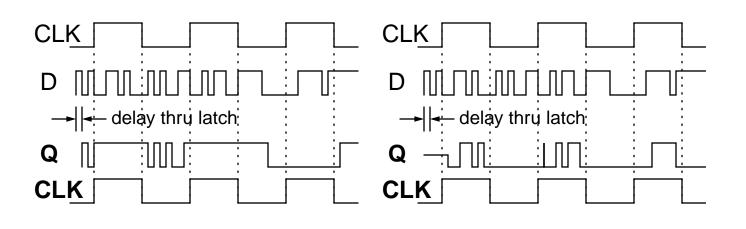

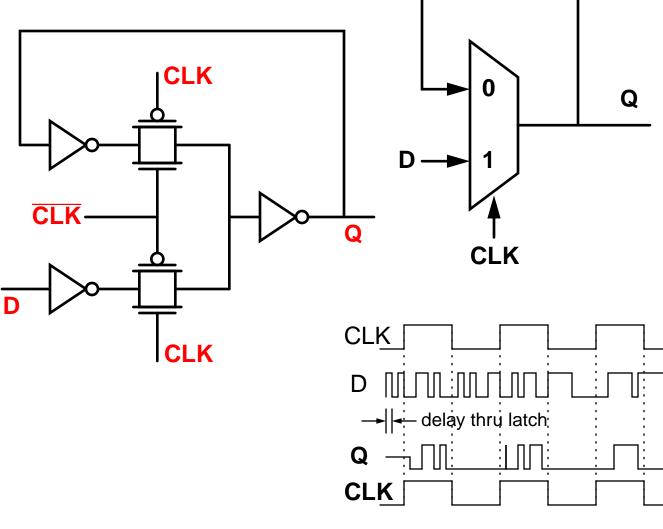

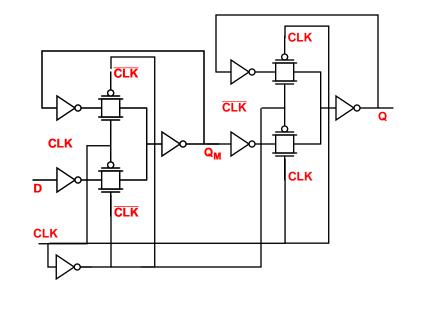

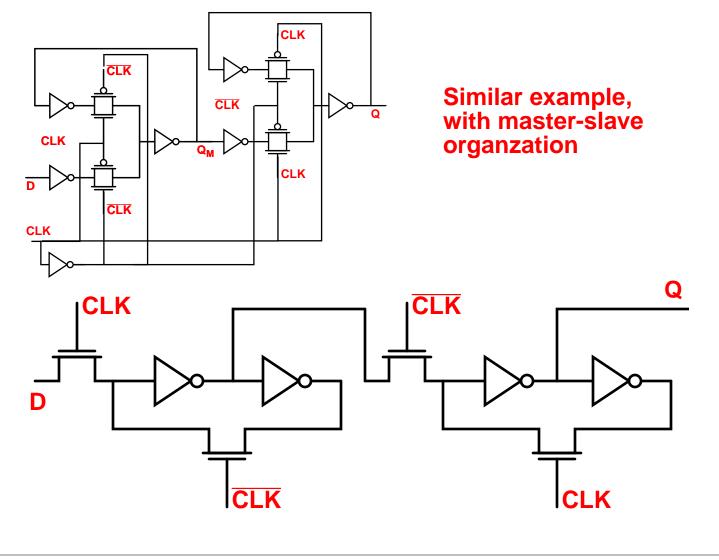

SLIDE 38

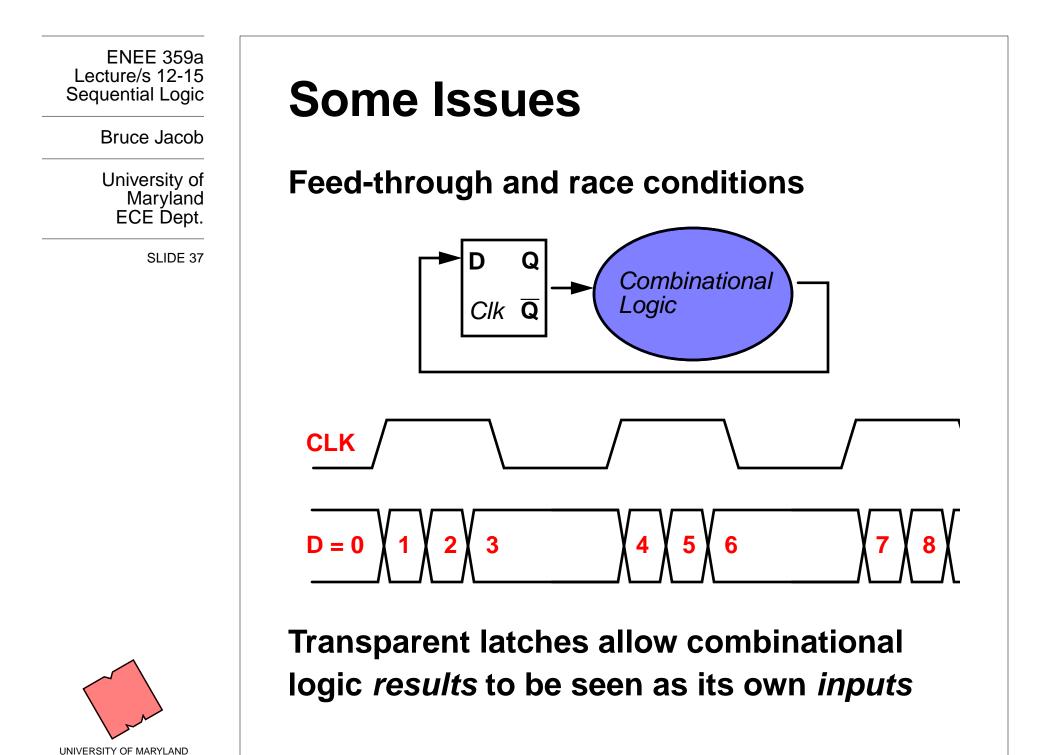

## **Some Issues**

Feed-through and race conditions

Master-slave D register (neg-edge triggered)

Bruce Jacob

University of Maryland ECE Dept.

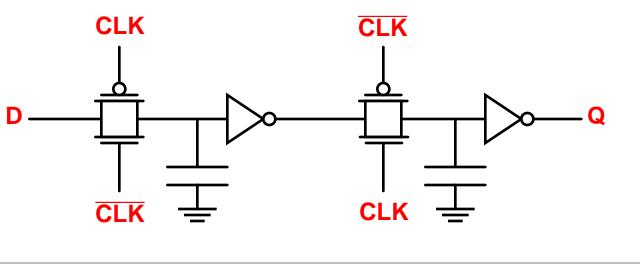

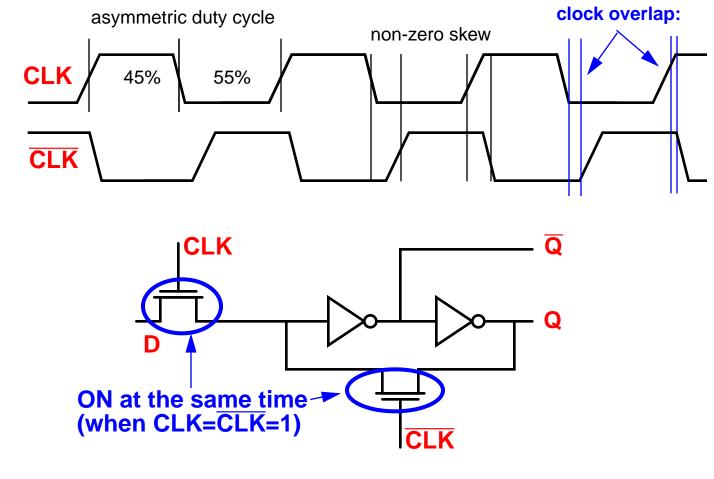

SLIDE 39

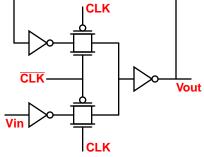

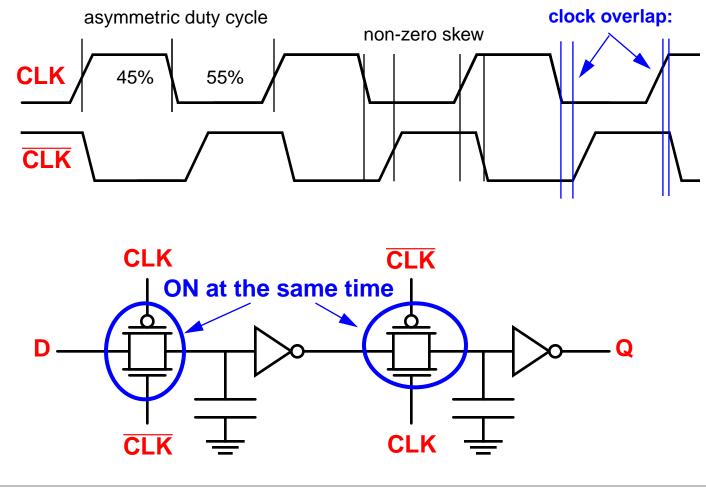

## Some Issues

### Cost of Clock Network (driving huge load)

Clock network drives 4 transistors per latch ... power-expensive. Alternative design:

- Design w/ NMOS pass transistors presents smaller load to CLK; INV can recover low "1" but at a cost

- However: requires non-overlapping CLK/CLK ... why?

#### Bruce Jacob

University of Maryland ECE Dept.

SLIDE 40

## **Some Issues**

#### Cost of Clock Network (driving huge load)

**Bruce Jacob**

University of Maryland ECE Dept.

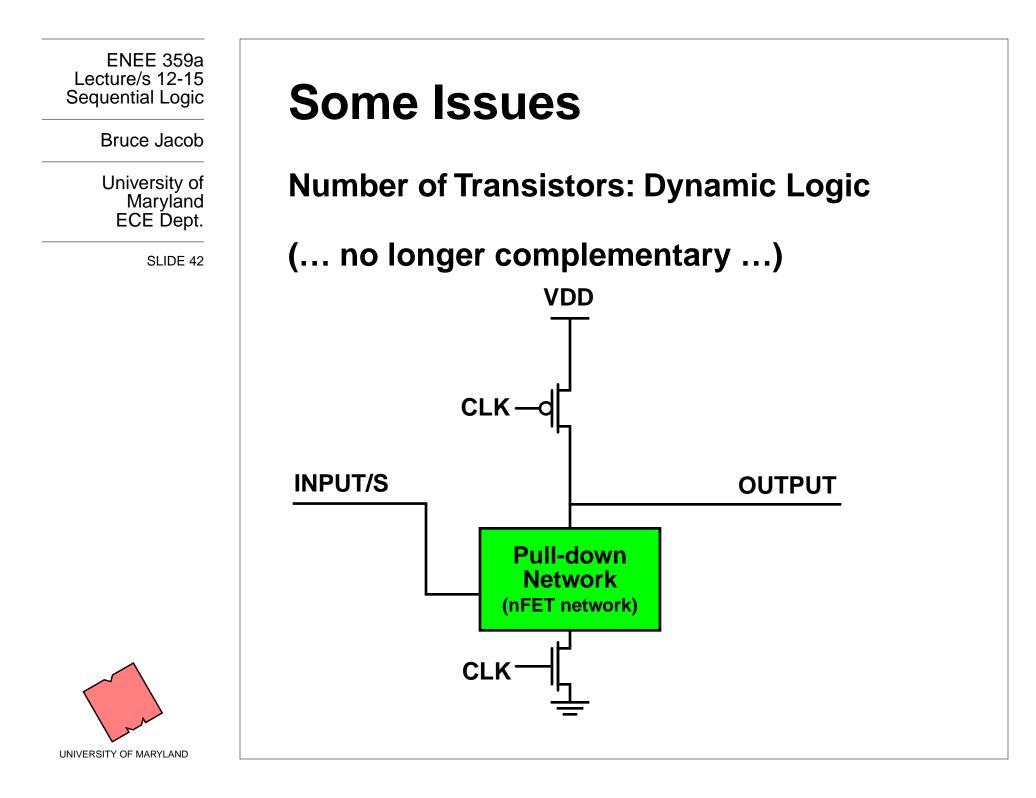

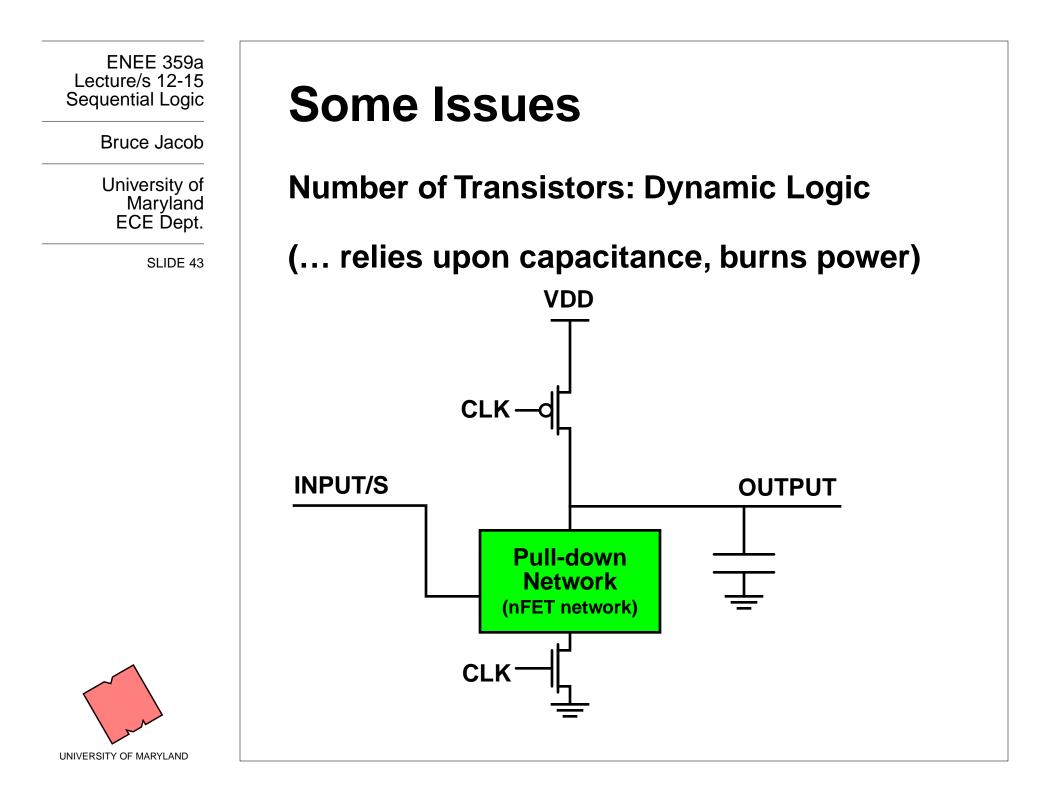

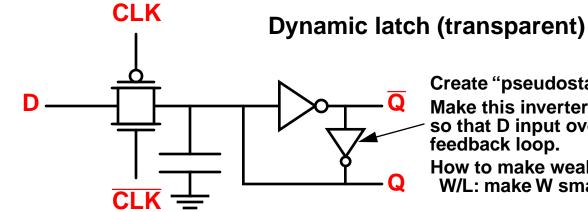

SLIDE 44

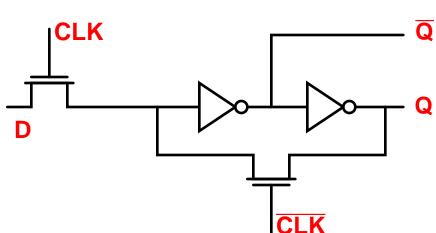

## Some Issues

#### Number of Transistors: *Dynamic* Storage

Create "pseudostatic" latch: Make this inverter weak so that D input overpowers How to make weak inverter:

W/L: make W small or L large

Dynamic edge-triggered register

Bruce Jacob

University of Maryland ECE Dept.

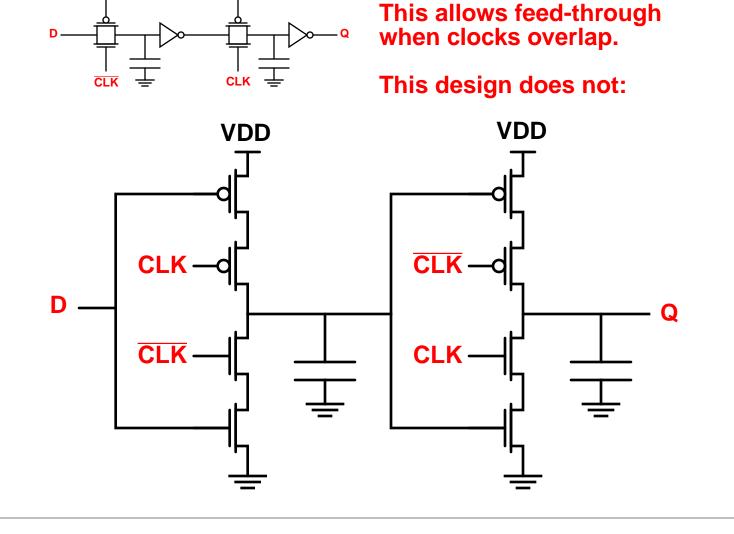

SLIDE 45

### **Some Issues**

**CLK**

CLK

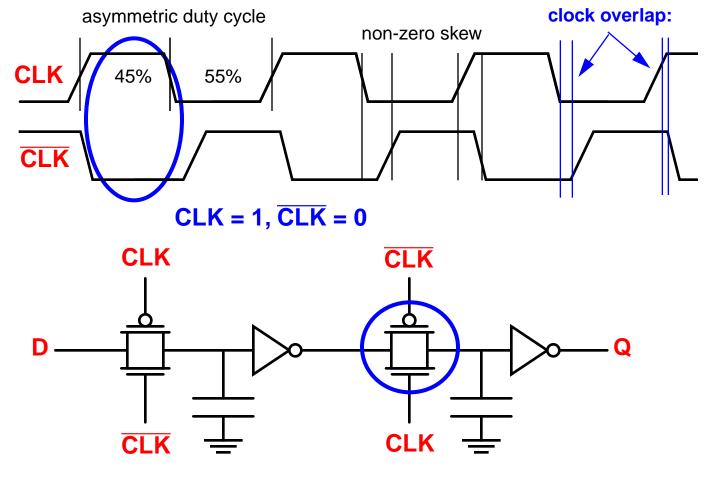

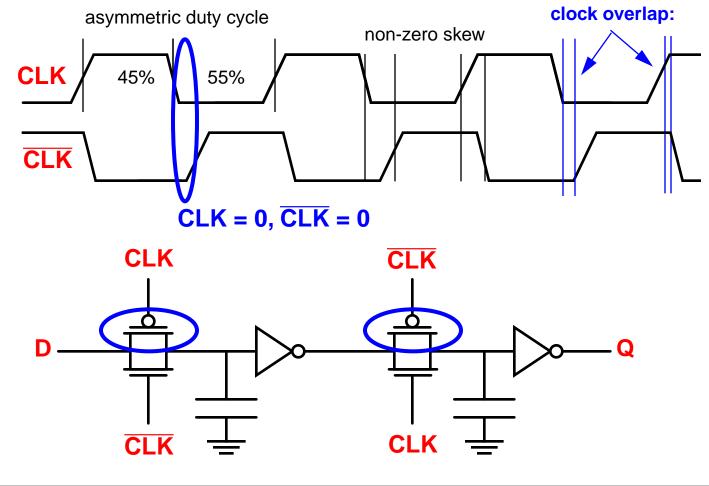

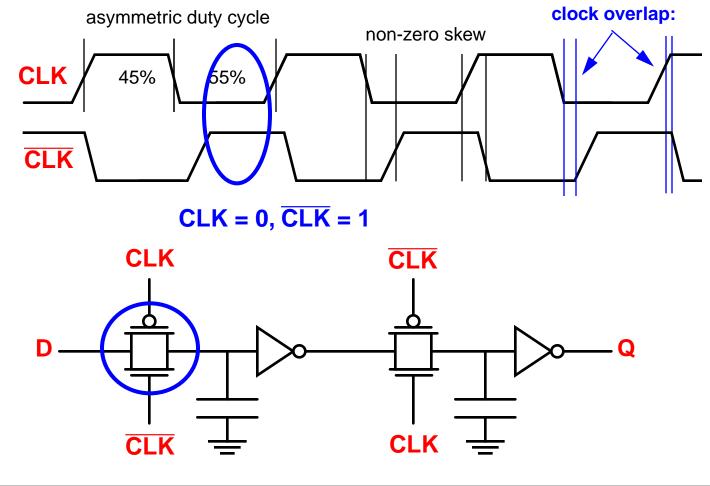

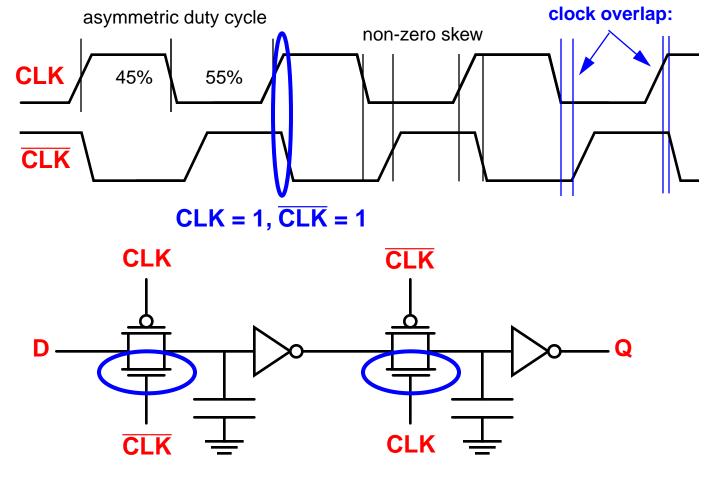

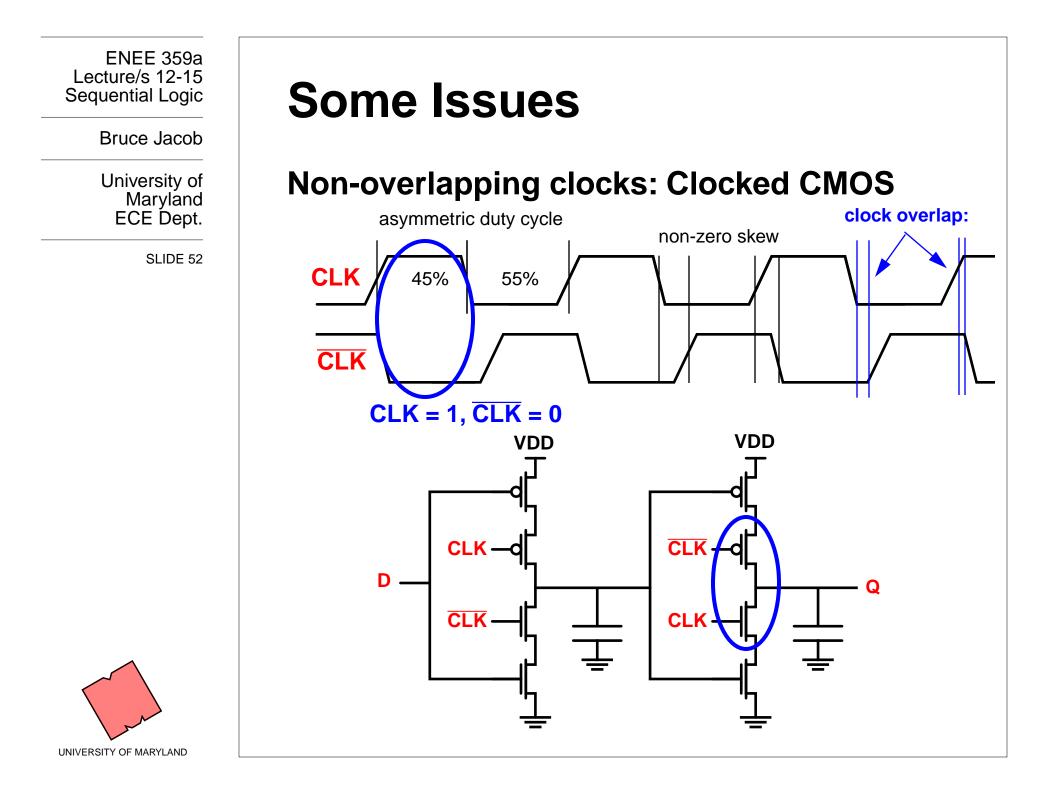

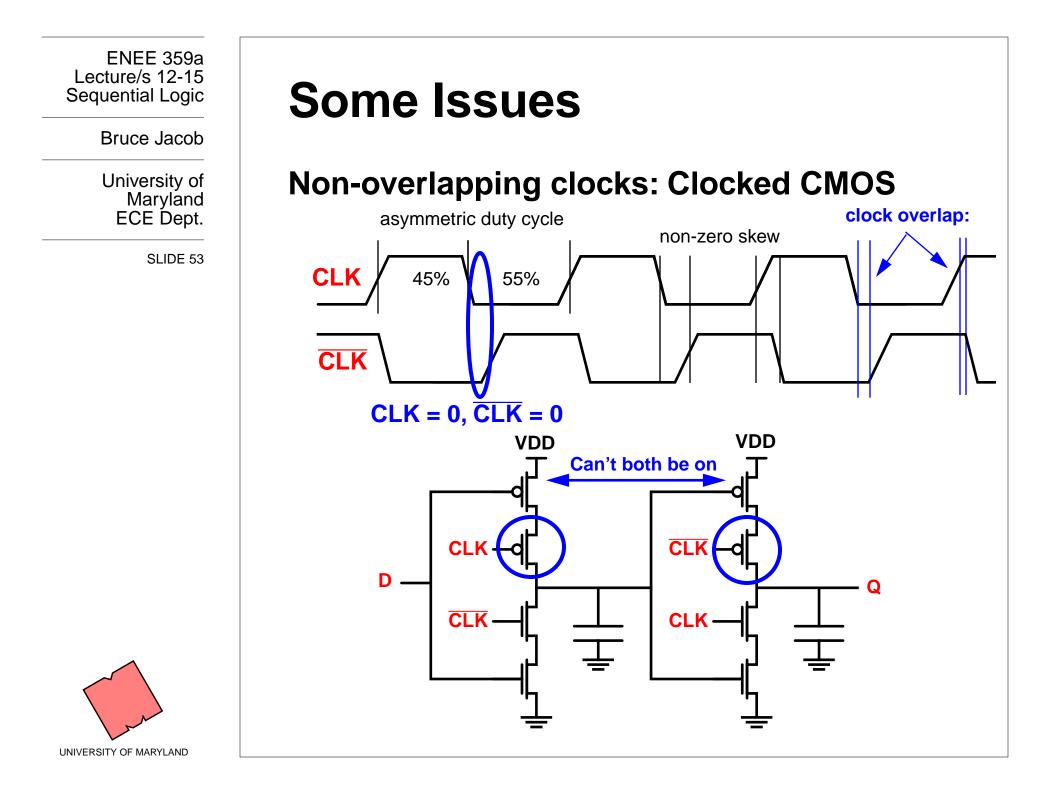

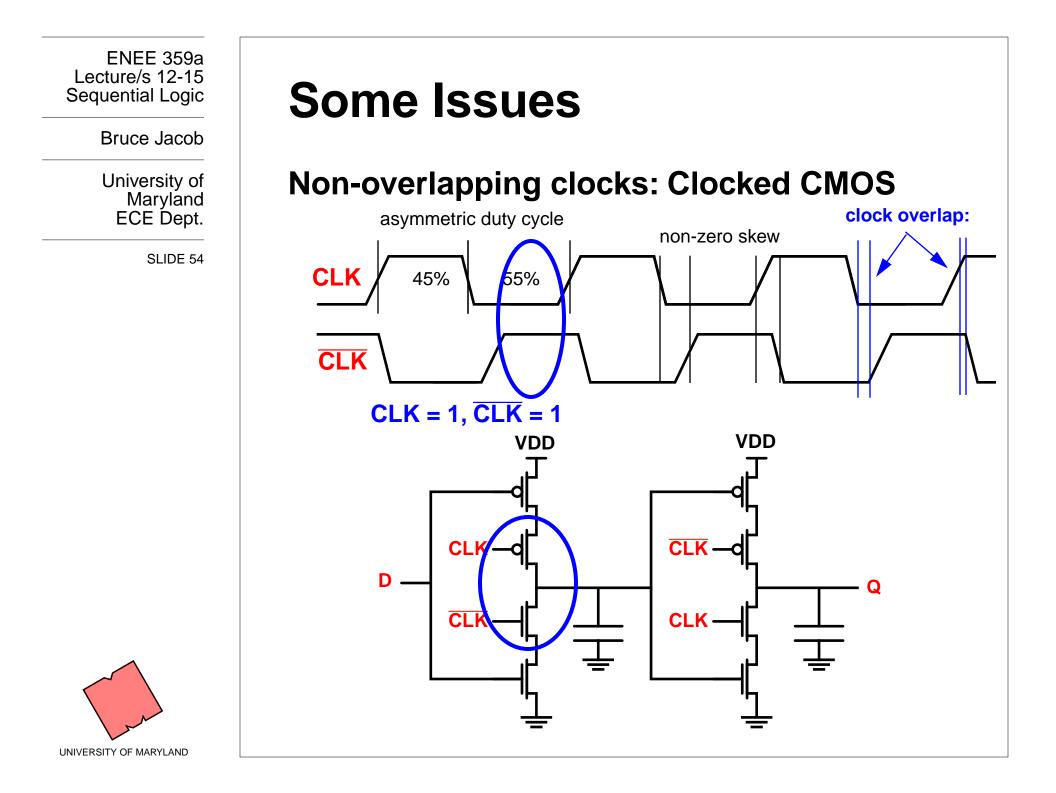

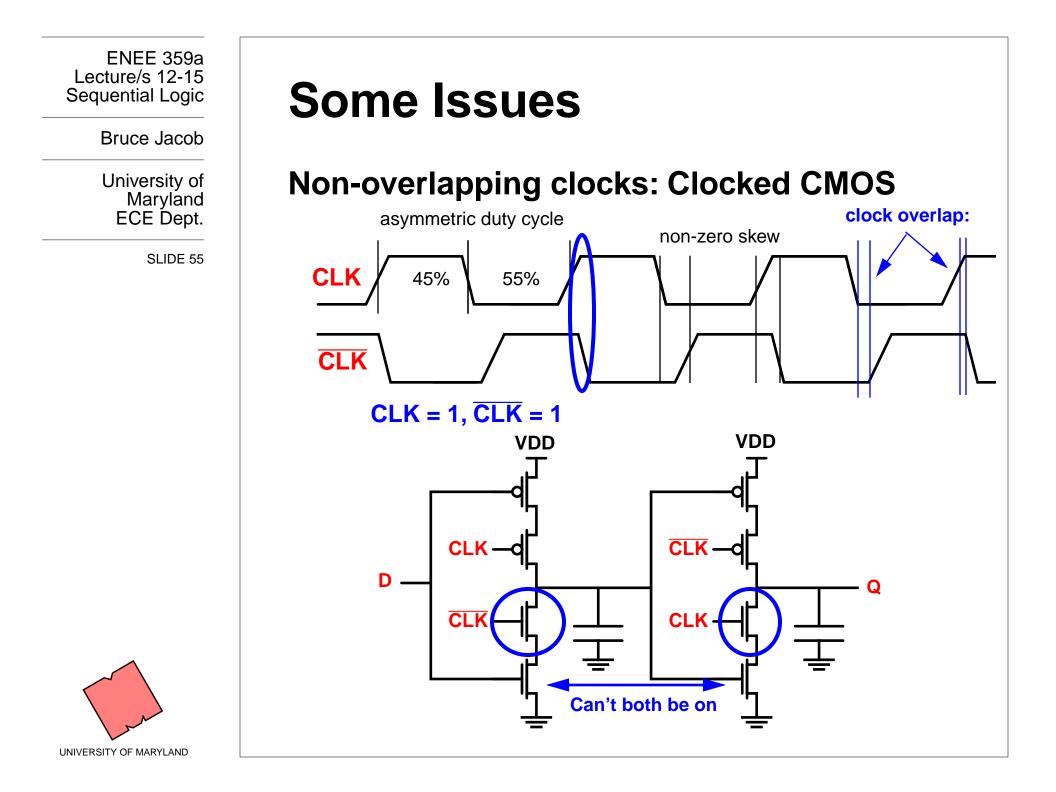

#### Non-overlapping clocks: Clocked CMOS

| ENEE 359a        |

|------------------|

| Lecture/s 12-15  |

| Sequential Logic |

University of Maryland ECE Dept.

SLIDE 46

# Some Issues

### Non-overlapping clocks: Clocked CMOS

| ENEE 359a        |

|------------------|

| Lecture/s 12-15  |

| Sequential Logic |

University of Maryland ECE Dept.

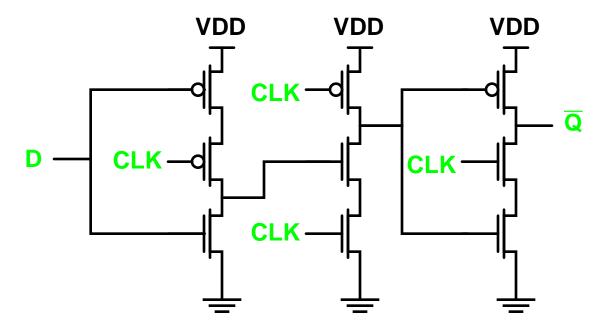

SLIDE 47

# Some Issues

### Non-overlapping clocks: Clocked CMOS

### **EXAMPLES:**

UNIVERSITY OF MARYLAND

| ENEE 359a        |

|------------------|

| Lecture/s 12-15  |

| Sequential Logic |

University of Maryland ECE Dept.

SLIDE 48

# Some Issues

### Non-overlapping clocks: Clocked CMOS

| ENEE 359a        |

|------------------|

| Lecture/s 12-15  |

| Sequential Logic |

University of Maryland ECE Dept.

SLIDE 49

### Non-overlapping clocks: Clocked CMOS

| ENEE 359a        |

|------------------|

| Lecture/s 12-15  |

| Sequential Logic |

University of Maryland ECE Dept.

SLIDE 50

# Some Issues

### Non-overlapping clocks: Clocked CMOS

| ENEE 359a        |

|------------------|

| Lecture/s 12-15  |

| Sequential Logic |

University of Maryland ECE Dept.

SLIDE 51

# Some Issues

### Non-overlapping clocks: Clocked CMOS

#### Bruce Jacob

University of Maryland ECE Dept.

SLIDE 56

### Some Issues

### Non-overlapping clocks: "True" Single-Phase Clocked Register

**Positive edge-driven register**

**Bruce Jacob**

University of Maryland ECE Dept.

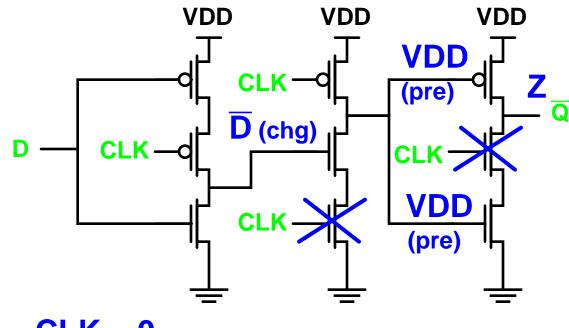

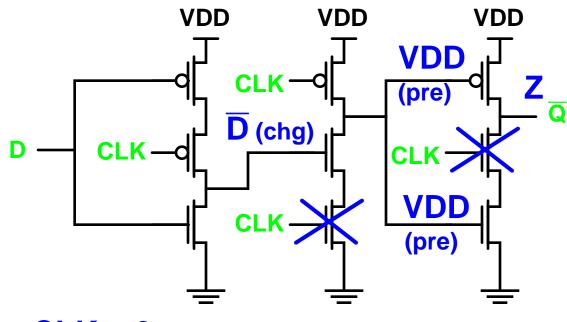

SLIDE 57

### Some Issues

### Non-overlapping clocks: "True" Single-Phase Clocked Register

CLK = 0

Output = Z => output is stable (dynamic)

**Bruce Jacob**

University of Maryland ECE Dept.

SLIDE 58

### Some Issues

### Non-overlapping clocks: "True" Single-Phase Clocked Register

#### Bruce Jacob

#### University of Maryland ECE Dept.

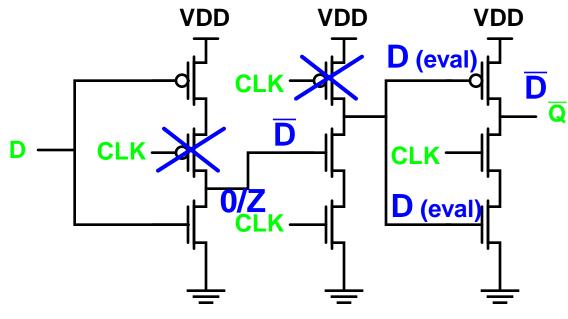

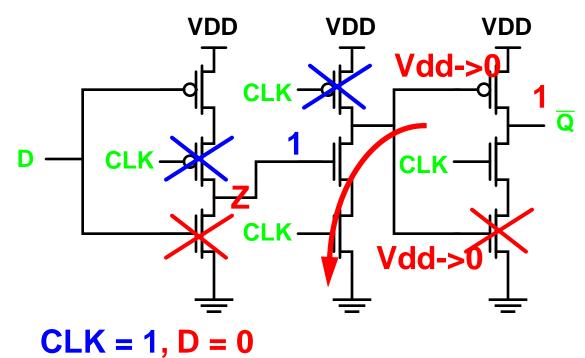

SLIDE 59

### Some Issues

### Non-overlapping clocks: "True" Single-Phase Clocked Register

### Some Issues

### Non-overlapping clocks: "True" Single-Phase Clocked Register

University of Maryland ECE Dept.

**Bruce Jacob**

SLIDE 60

#### Bruce Jacob

University of Maryland ECE Dept.

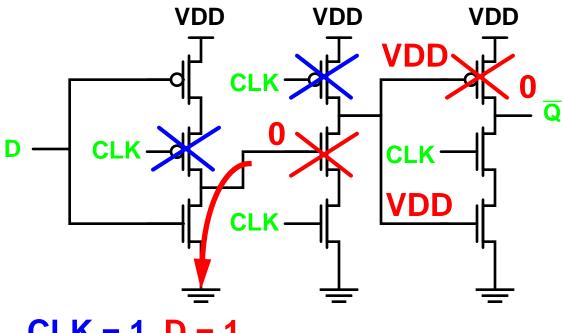

SLIDE 61

### **Some Issues**

### Non-overlapping clocks: "True" Single-Phase Clocked Register

**CLK = 1, D = 1**

#### Bruce Jacob

University of Maryland ECE Dept.

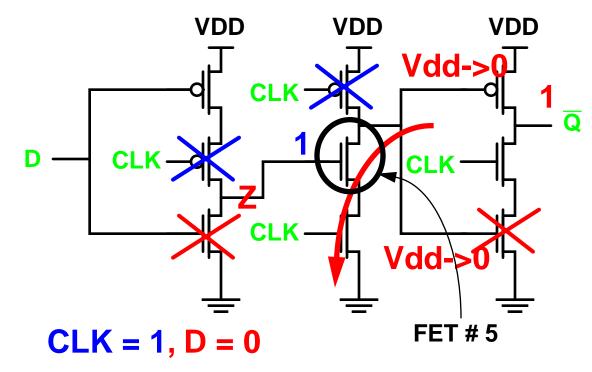

SLIDE 62

### Some Issues

### Non-overlapping clocks: "True" Single-Phase Clocked Register

Note: if D is allowed to transition from 0 to 1 too soon after CLK transitions  $0 \rightarrow 1$ , it is possible to close FET #5 before the final capacitance discharges  $(Vdd \rightarrow 0)$  ... which would obviously pose a problem.

This represents the hold time of this register.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 63

## Some Issues

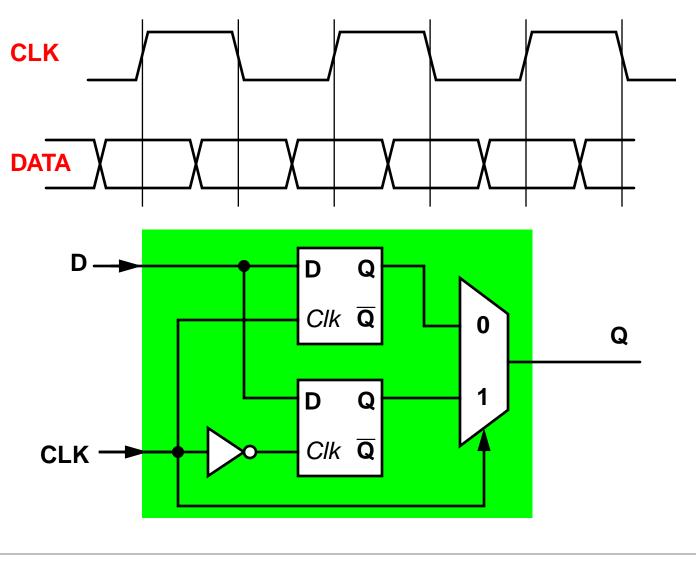

**Clock power: Dual-Edge-Triggered Reg.**

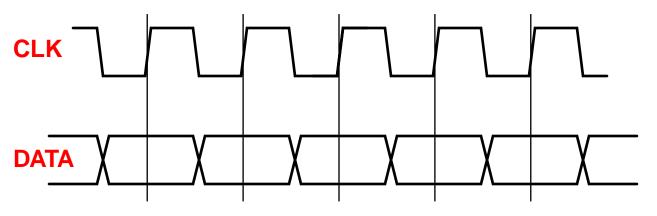

Note that clock transitions twice as often as data does (actually, even more, unless the data pattern happens to be 0101010101010 ...)

Max data rate = 1Gbps; clock rate = 2GHz

At high frequencies, this is a problem

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 64

## **Some Issues**

Clock power: Dual-Edge-Triggered Reg.

#### Bruce Jacob

University of Maryland ECE Dept.

SLIDE 65

## Some Issues

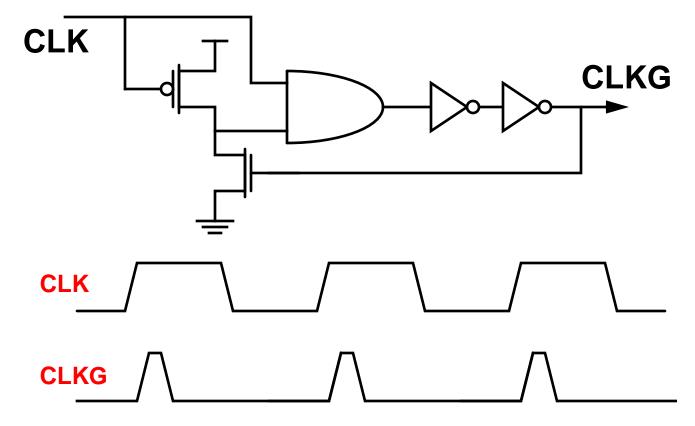

Simplicity, speed of design: Pulse registers

For use with transparent latches: creates *de facto* registers, provided you do thorough timing analysis to guarantee inputs to latch stable during transparent window.

Benefits: latches much faster than registers, use fewer transistors, present lighter load to clock network (leads to lower power consumption).

Bruce Jacob

University of Maryland ECE Dept.

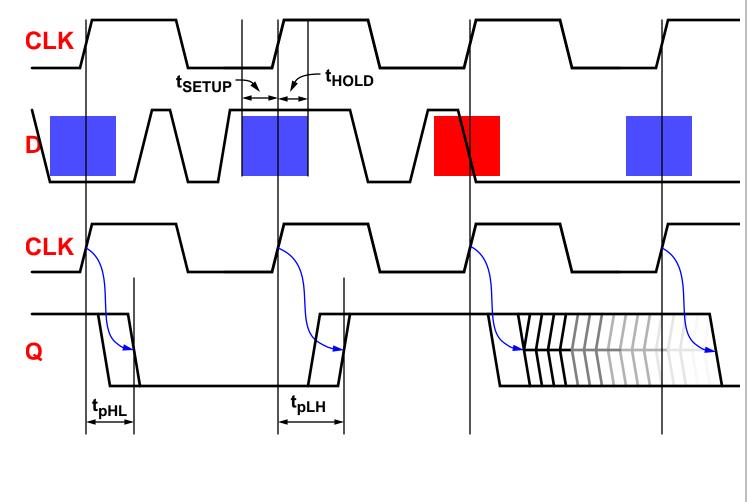

SLIDE 66

## **Some Issues**

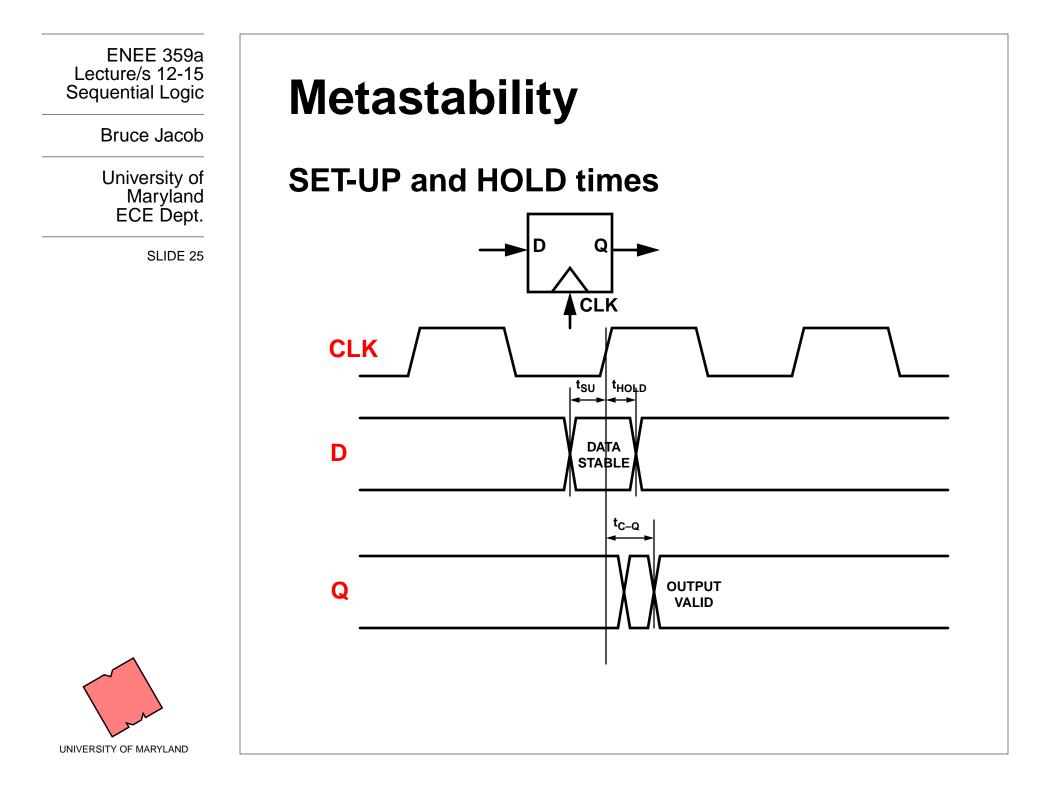

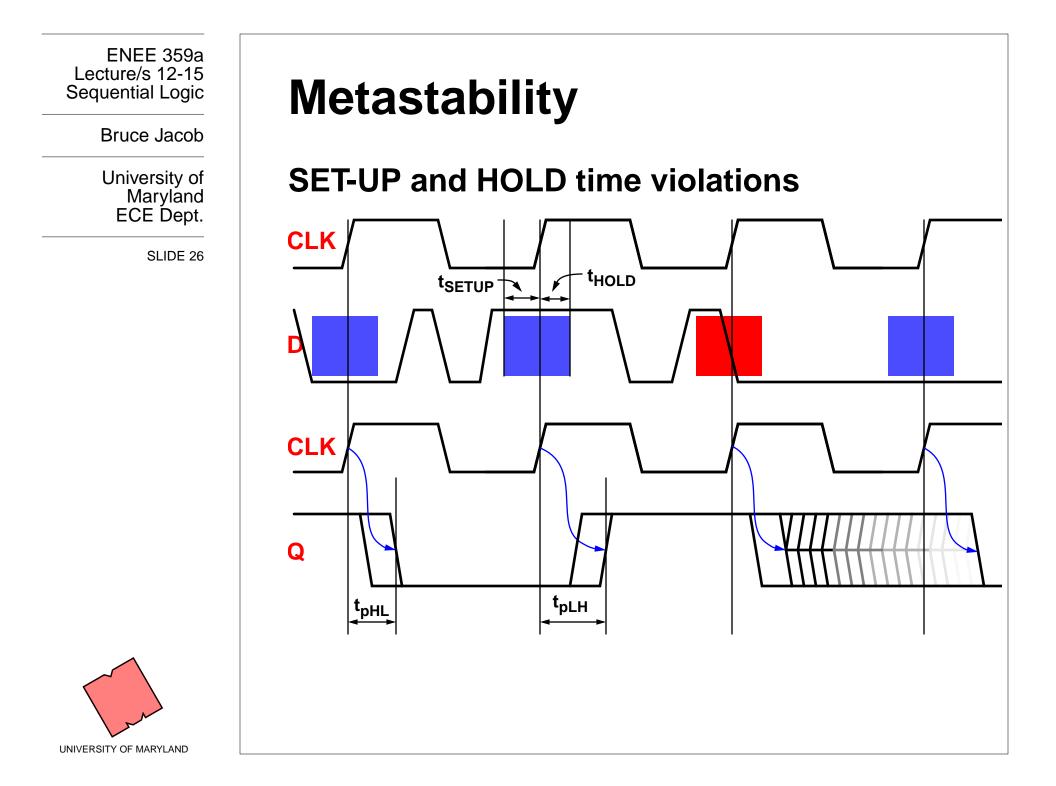

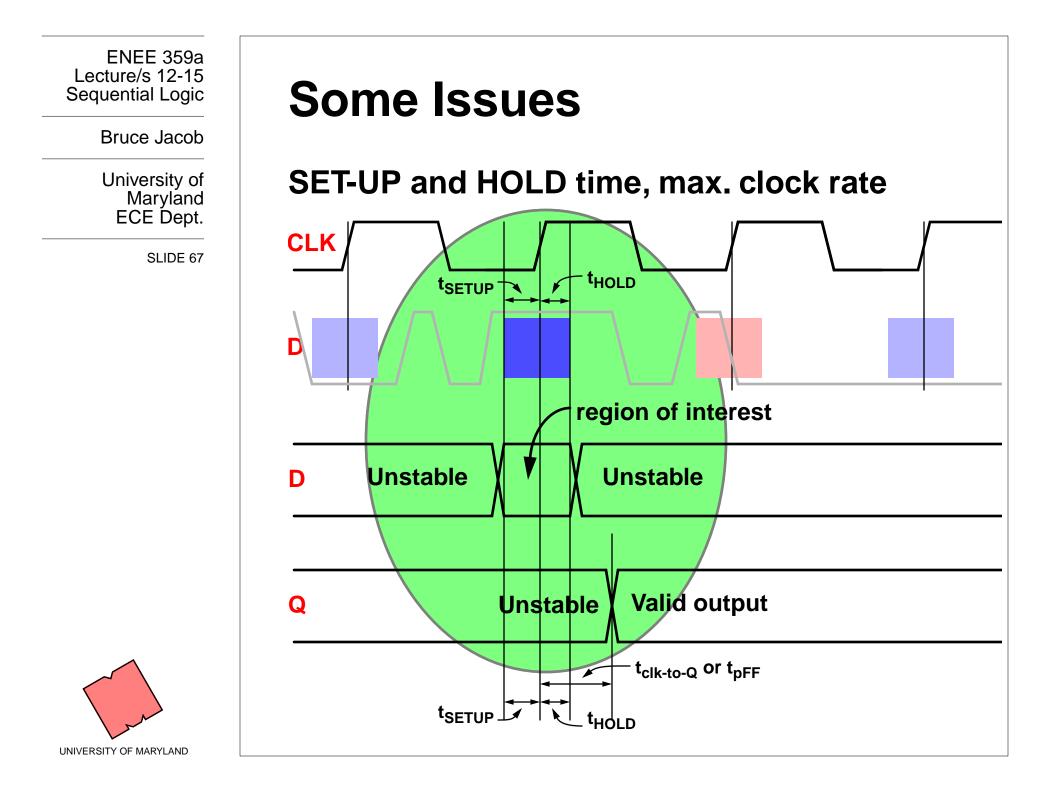

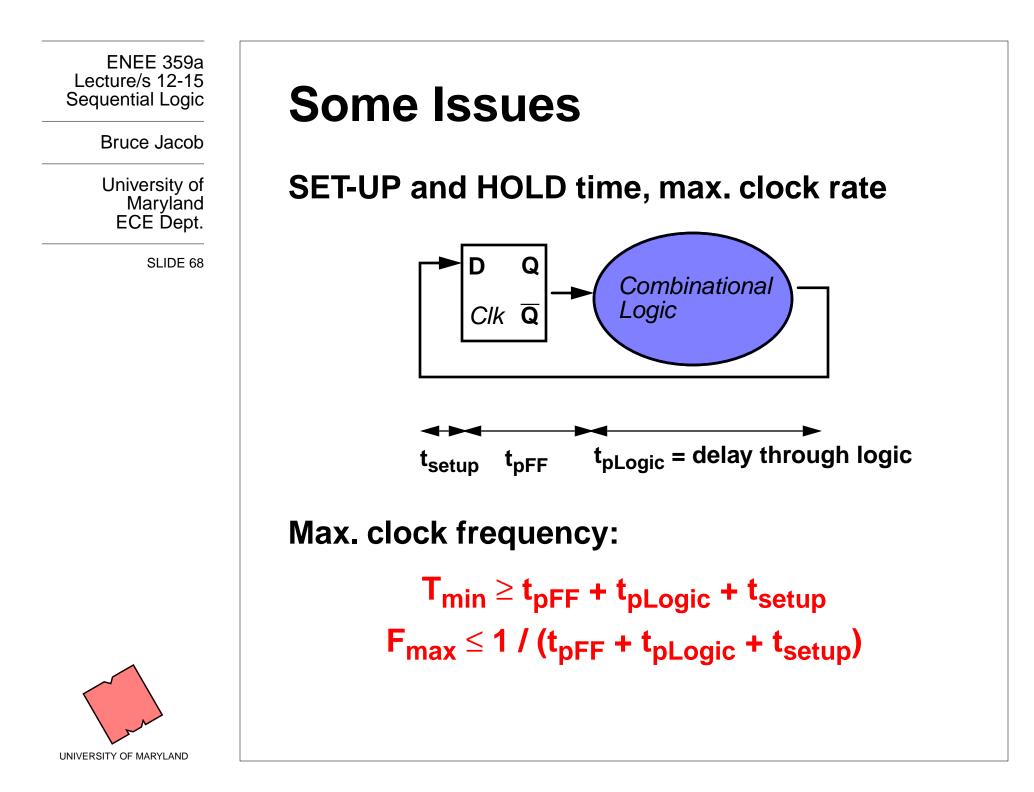

#### **SET-UP and HOLD time, metastability**

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 69

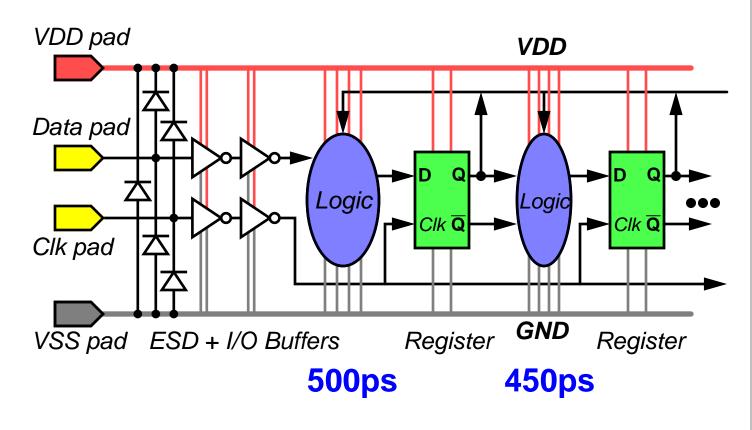

# Pipelining

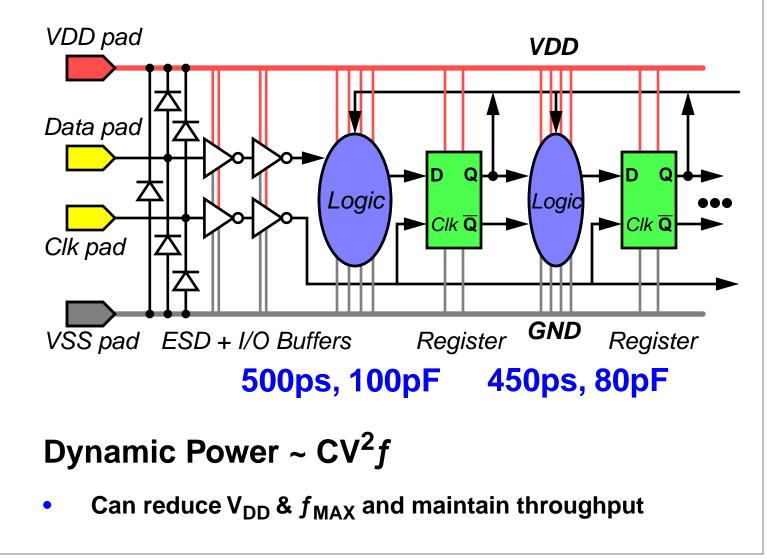

#### Goal: Increase max. clock rate

Worst-case logic delay: 950ps vs. 500ps

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 70

# Pipelining

### **Goal: Decrease power dissipation**