Bruce Jacob

University of Maryland ECE Dept.

SLIDE 1

## ENEE 359a Digital VLSI Design

# Transistor Sizing & Logical Effort

Prof. Bruce Jacob blj@ece.umd.edu

Credit where credit is due:

Slides contain original artwork (© Jacob 2004) as well as material taken liberally from Irwin & Vijay's CSE477 slides (PSU), Schmit & Strojwas's 18-322 slides (CMU), Dally's EE273 slides (Stanford), Wolf's slides for *Modern VLSI Design*, and/or Rabaey's slides (UCB).

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 2

# **Overview**

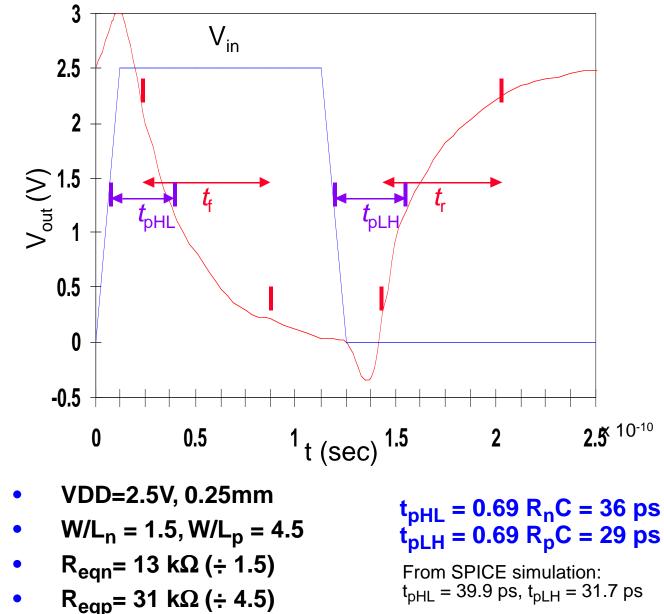

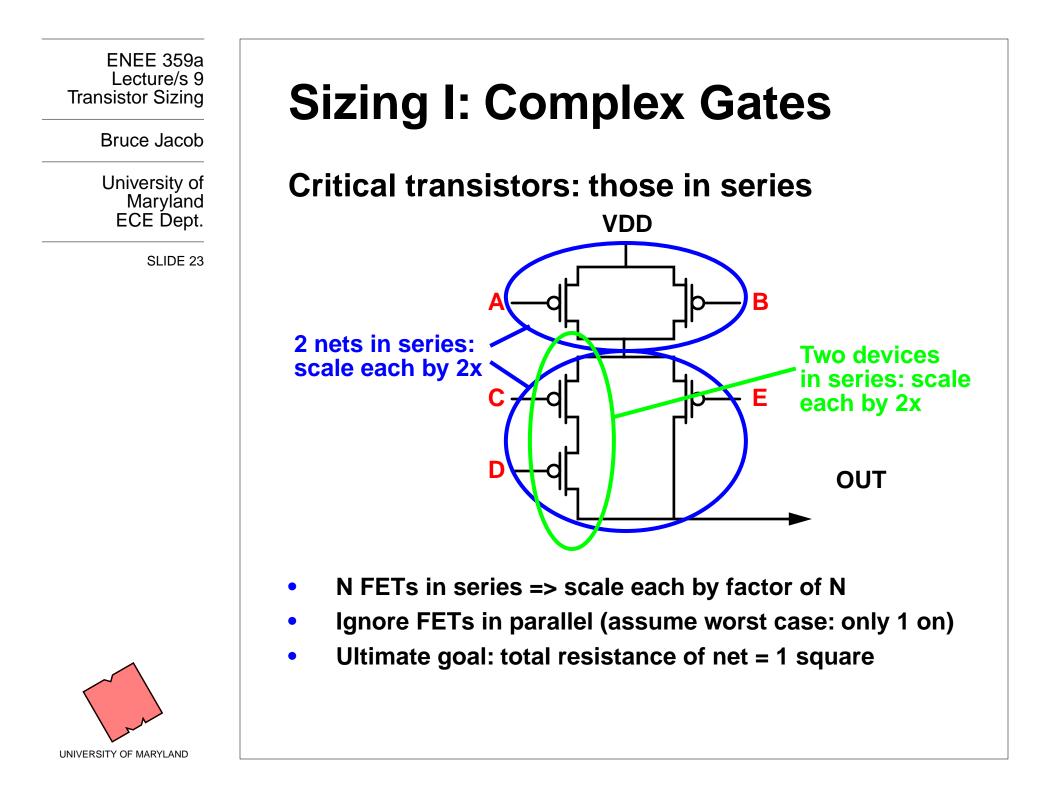

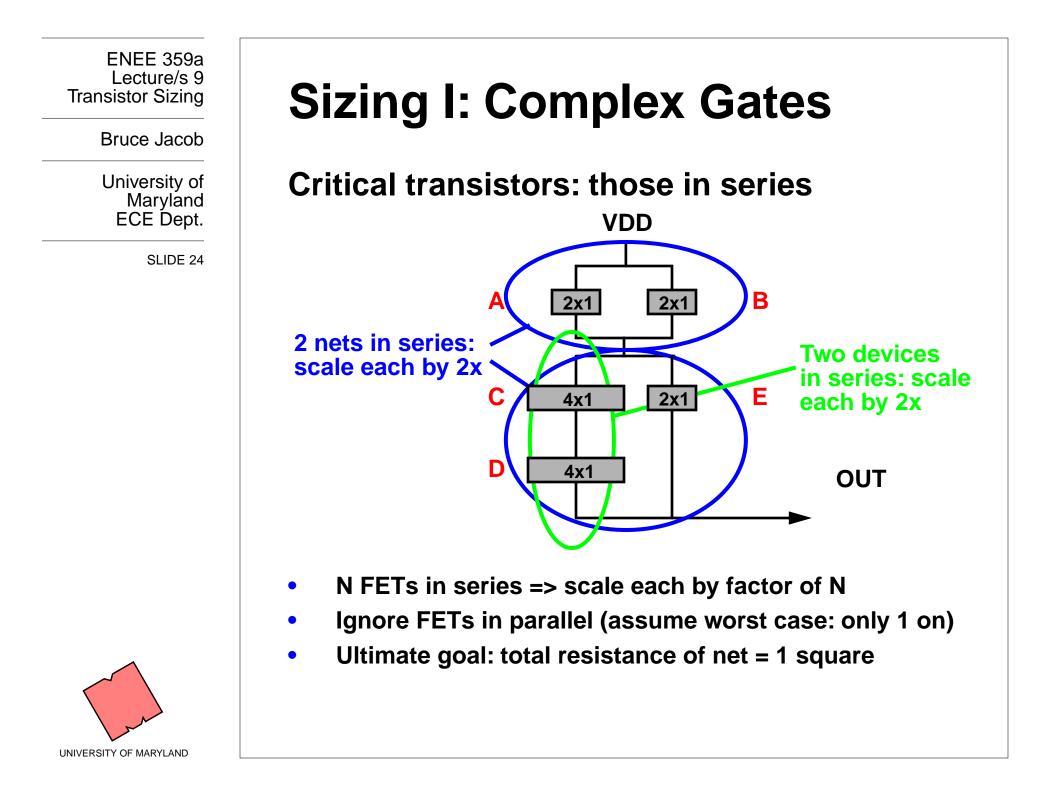

- Sizing of transistors to balance performance of single inverter

- More on RC time constant, first-order approximation of time delays

- Sizing in complex gates, examples

- Sizing of inverter chains for driving high capacitance loads (off-chip wires)

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 4

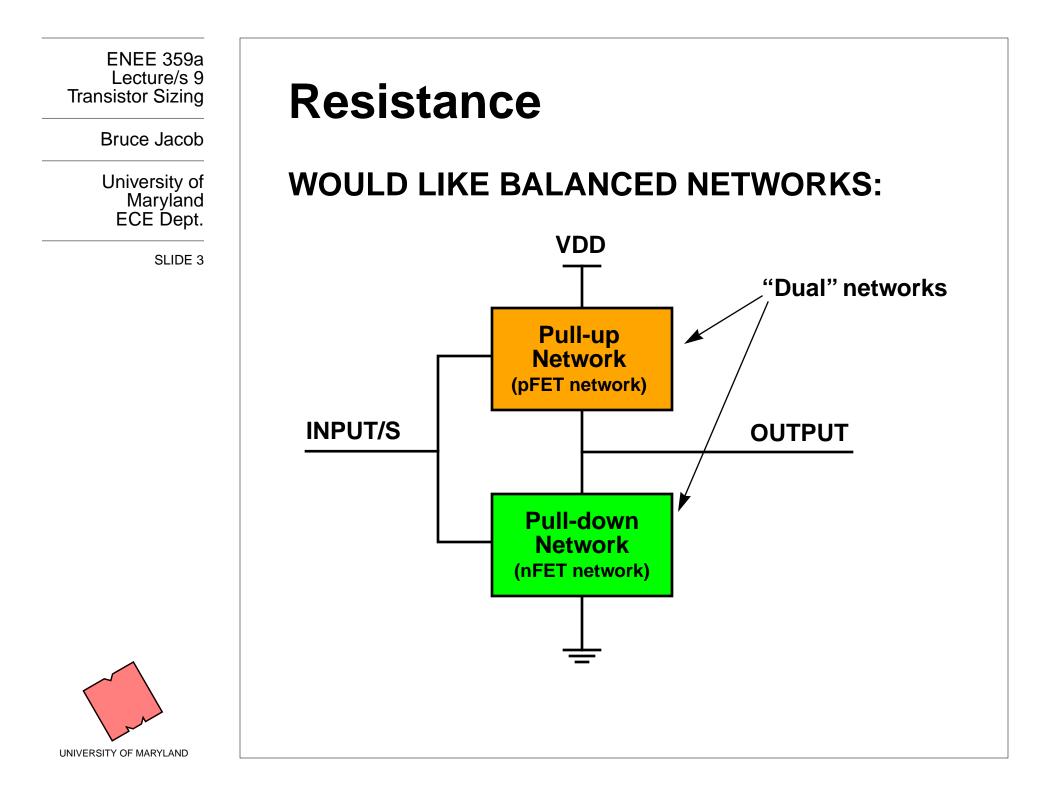

# Resistance

**Resistance of MOSFET:**

$$\boldsymbol{R}_{n} = \frac{1}{\mu_{n} \boldsymbol{C}_{ox} (\boldsymbol{V}_{GS} - \boldsymbol{V}_{Tn})} \left(\frac{\boldsymbol{L}}{\boldsymbol{W}}\right)$$

Increasing W decreases the resistance; allows more current to flow

Oxide capacitance  $C_{ox} = \epsilon_{ox} / t_{ox}$  [F/cm<sup>2</sup>]

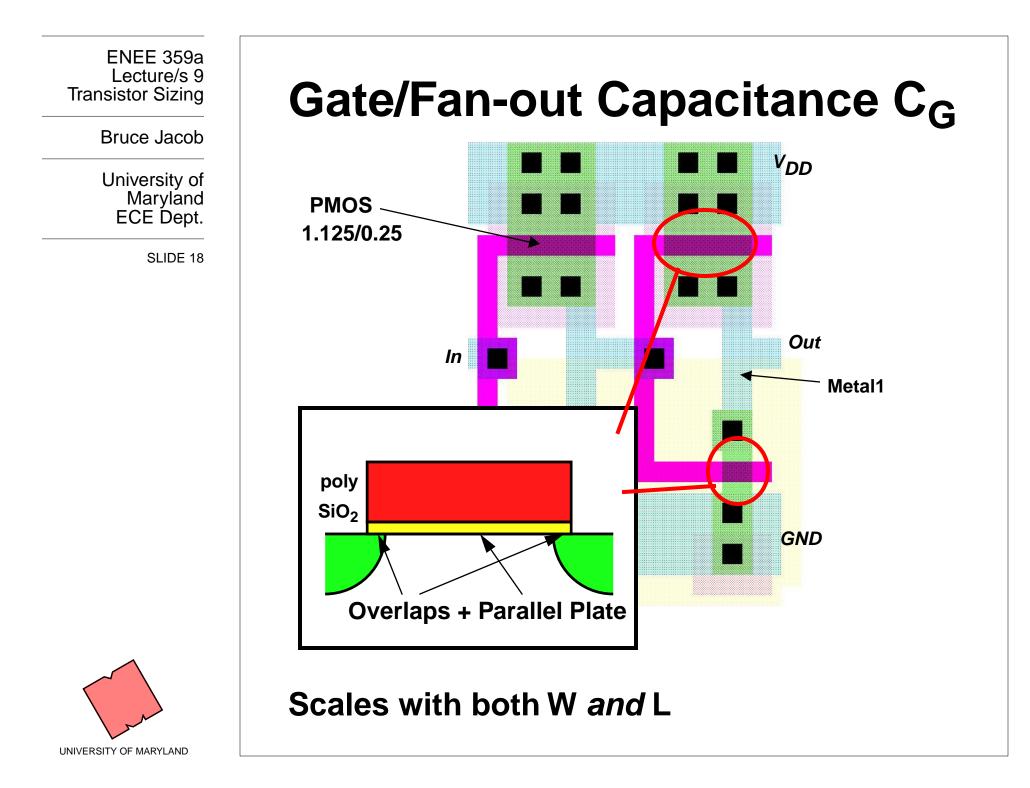

Gate capacitance  $C_{\rm G} = C_{\rm ox} WL$  [F]

Transconductance  $\beta_n = \mu_n C_{ox} \left( \frac{W}{L} \right) = k'_n \left( \frac{W}{L} \right)$

(units [A/V<sup>2</sup>])

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 5

# Resistance

## nFET vs. pFET

$$R_{n} = \frac{1}{\beta_{n}(V_{DD} - V_{Tn})} \qquad \beta_{n} = \mu_{n}C_{ox}\left(\frac{W}{L}\right)_{n}$$

$$R_{p} = \frac{1}{\beta_{p}(V_{DD} - |V_{Tp}|)} \qquad \beta_{p} = \mu_{p}C_{ox}\left(\frac{W}{L}\right)_{p}$$

$\mu_{p}$

(µ is the carrier mobility through device)

(2..3)

RC circuit's respose to step input ... time for output to reach 50% value ... more detail on this in a moment, after we discuss *capacitance* ...)

UNIVERSITY OF MARYLAND

#### ENEE 359a Lecture/s 9 Transistor Sizing Bruce Jacob University of Maryland ECE Dept. SLIDE 8

- R = pl/A = pl/(wh) for rectangular wires (on-chip wires & vias, PCB traces)

- $R = \rho I/A = \rho I/(\pi r^2)$  for circular wires (off-chip, off-PCB)

| Material Resistivity ρ (Ω |            |

|---------------------------|------------|

| Silver (Ag)               | 1.6 x 10-8 |

| Copper (Cu)               | 1.7 x 10-8 |

| Gold (Au)                 | 2.2 x 10-8 |

| Aluminum (Al)             | 2.7 x 10-8 |

| Tungsten (W)              | 5.5 x 10-8 |

UNIVERSITY OF MARYLAND

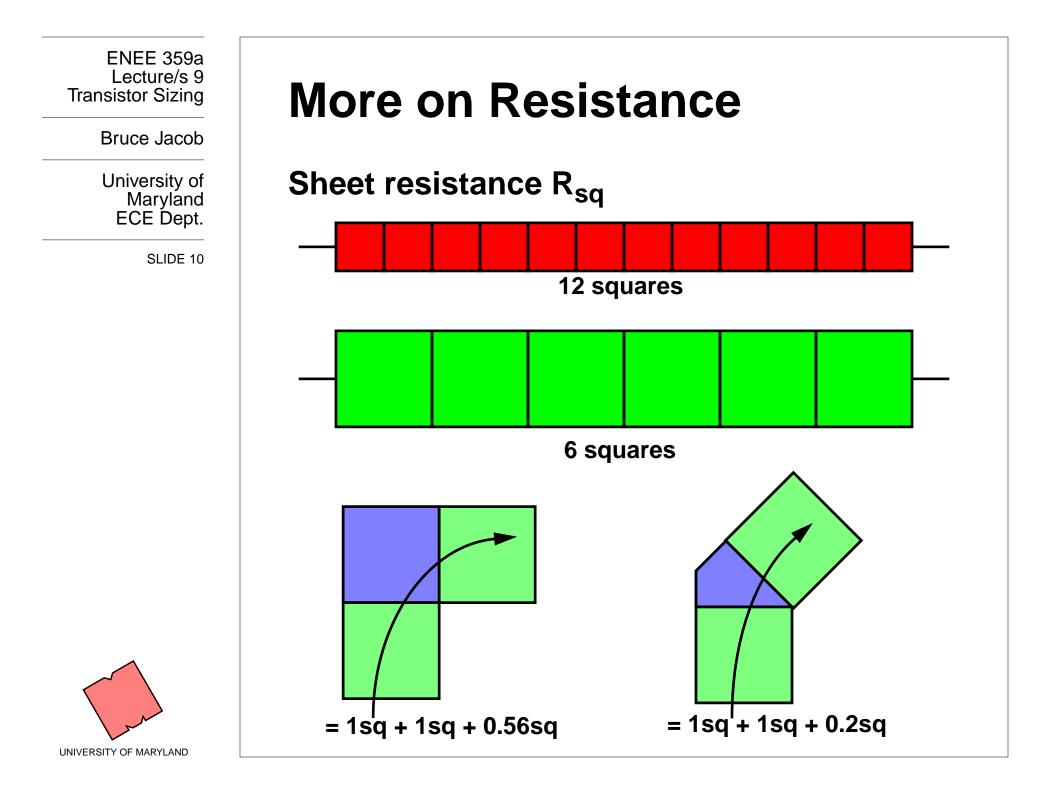

# **Sheet Resistance**

$R = \rho l/(wh) = l/w \cdot \rho/h$  for rectangular wires Sheet resistance  $R_{sq} = \rho/h$  (*h=thickness*)

| Material                  | Sheet resistance R <sub>sq</sub> (Ω/sq) |  |

|---------------------------|-----------------------------------------|--|

| n, p well diffusion       | 1000 to 1500                            |  |

| n+, p+ diffusion          | 50 to 150                               |  |

| polysilicon               | 150 to 200                              |  |

| polysilicon with silicide | 4 to 5                                  |  |

| Aluminum                  | 0.05 to 0.1                             |  |

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

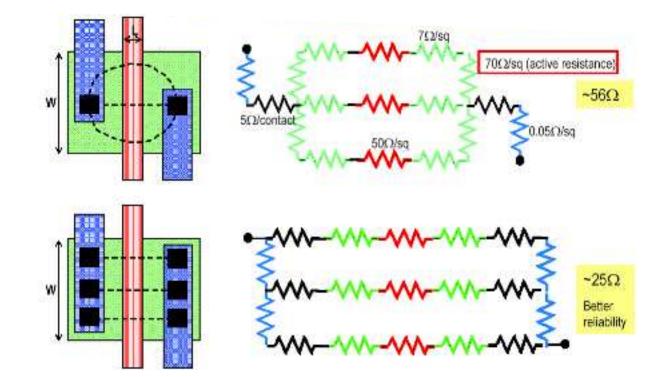

# More on Resistance

#### (it's not just the channel that counts)

SLIDE 11

ENEE 359a Lecture/s 9

**Bruce Jacob**

University of \_\_\_\_\_\_\_\_ Maryland

ECE Dept.

**Transistor Sizing**

# And Now ... Capacitance (C<sub>L</sub>)

- intrinsic MOS transistor capacitances

- extrinsic MOS transistor (fanout) capacitances

- wiring (interconnect) capacitance

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 13

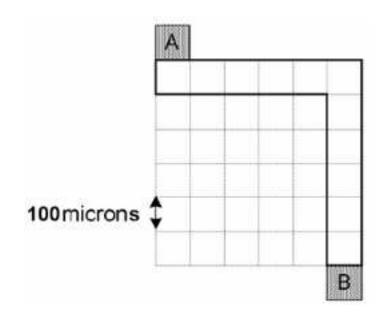

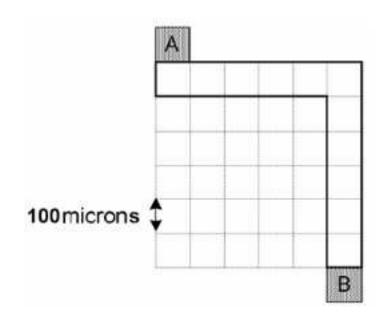

# C<sub>W</sub>, a Large Example

Given: R = 40 mΩ/□ C<sub>tringe</sub> = 0.044 fF/μm C<sub>plate</sub> = 0.031 fF/μm<sup>2</sup>

#### Determine:

the resistance between A and B, the plate and fringe capacitances to ground.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 14

# C<sub>W</sub>, a Large Example

Given: R = 40 mΩ/□ C<sub>tringe</sub> = 0.044 fF/μm C<sub>plate</sub> = 0.031 fF/μm<sup>2</sup>

#### Determine:

the resistance between A and B, the plate and fringe capacitances to ground.

```

\label{eq:response} \begin{array}{l} \mathsf{R} = (9+2*\ 0.56\ \text{squares}) *\ 40\ \text{m}\Omega/\Box = \ 404.8\ \text{m}\Omega \\ \mathsf{C}_{\text{tringe,g}} = \mathsf{Perimeter}\ \mathsf{C}_{\text{tringe}} = 96.8\text{fF} \\ (\mathsf{Perimeter} = 2200\ \mu\text{m}) \\ \mathsf{C}_{\text{plate,g}} = \mathsf{Area}\ \mathsf{C}_{\text{plate}} = 3.41\text{pF} \\ (\mathsf{Area} = 110,000\ \mu\text{m}^2) \end{array}

```

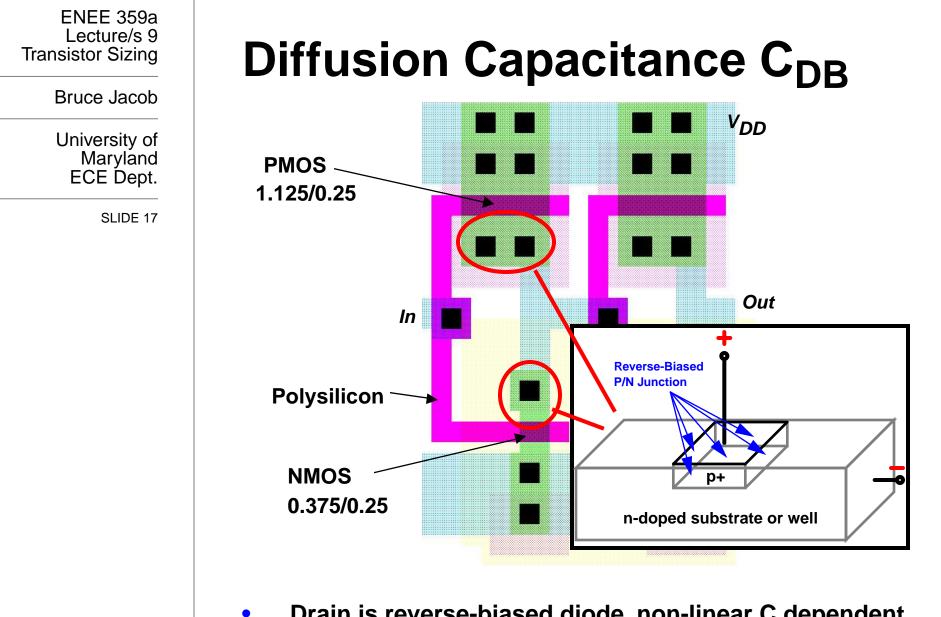

Drain is reverse-biased diode, non-linear C dependent on drain voltage (approx. nonlinearity with linear eqn, using K terms for bottom plate and sidewalls)

UNIVERSITY OF MARYLAND

| ENEE 359a         |

|-------------------|

| Lecture/s 9       |

| Transistor Sizing |

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 19

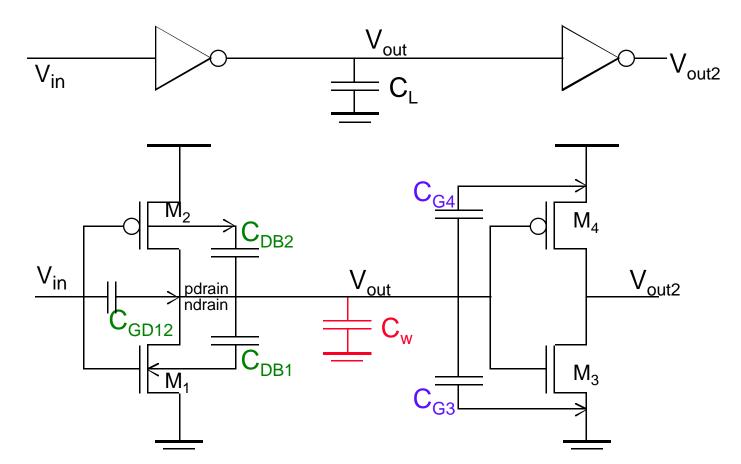

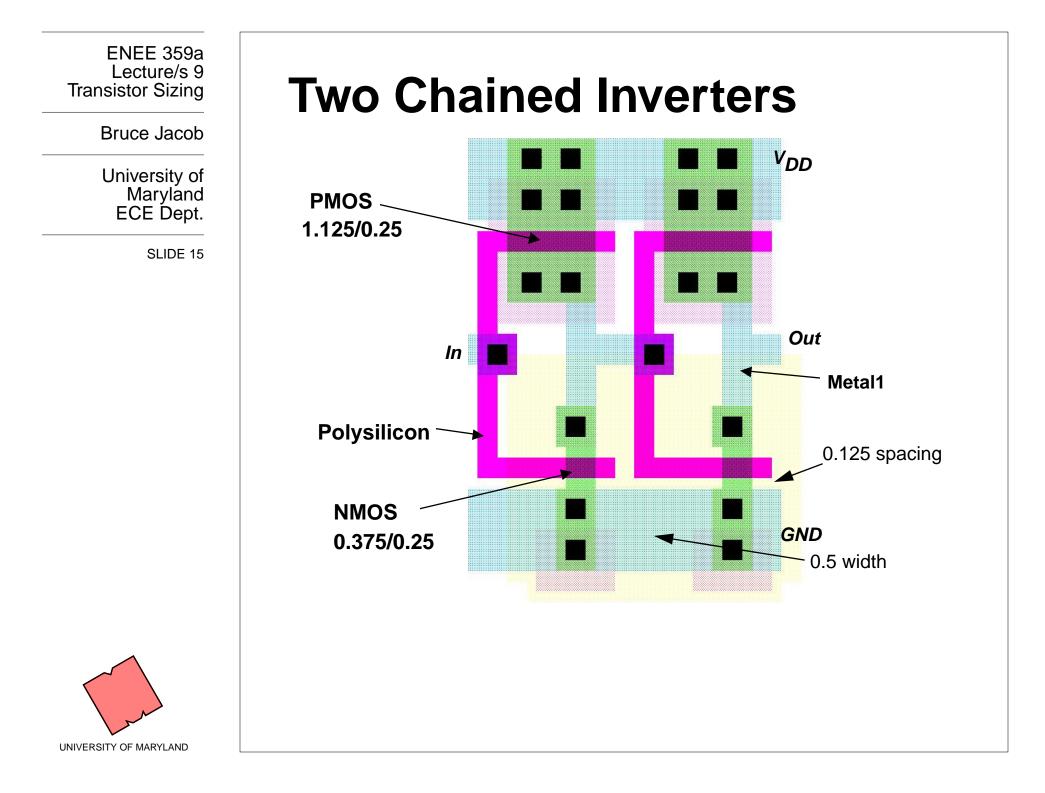

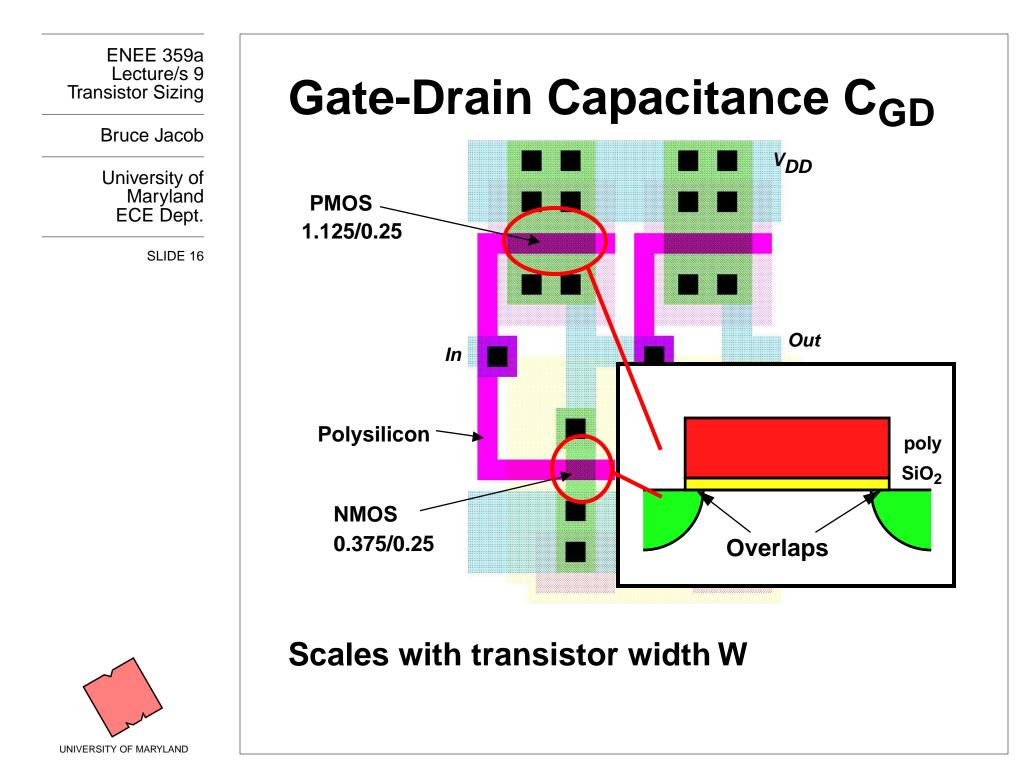

# **Two Chained Inverters: CL**

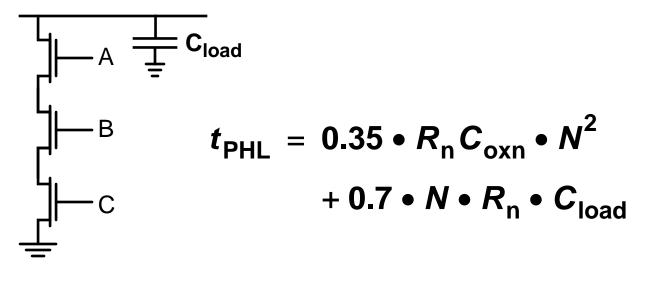

| C Term           | Expression                                | Value (fF)<br>H $\rightarrow$ L | Value (fF)<br>L $\rightarrow$ H |

|------------------|-------------------------------------------|---------------------------------|---------------------------------|

| C <sub>GD1</sub> | 2 C <sub>on</sub> W <sub>n</sub>          | 0.23                            | 0.23                            |

| C <sub>GD2</sub> | 2 C <sub>op</sub> W <sub>p</sub>          | 0.61                            | 0.61                            |

| C <sub>DB1</sub> | $K_{eqbpn}AD_nC_j + K_{eqswn}PD_nC_{jsw}$ | 0.66                            | 0.90                            |

| C <sub>DB2</sub> | $K_{eqbpp}AD_pC_j + K_{eqswp}PD_pC_{jsw}$ | 1.50                            | 1.15                            |

| C <sub>G3</sub>  | $2 C_{on} W_{n} + C_{ox} W_{n} L_{n}$     | 0.76                            | 0.76                            |

| C <sub>G4</sub>  | $2 C_{op} W_{p} + C_{ox} W_{p} L_{p}$     | 2.28                            | 2.28                            |

| C <sub>W</sub>   | From extraction                           | 0.12                            | 0.12                            |

| CL               | Sum                                       | 6.1                             | 6.0                             |

- Terms in red: under control of designer

- C<sub>L</sub> split between intrinsic and extrinsic/wire sources

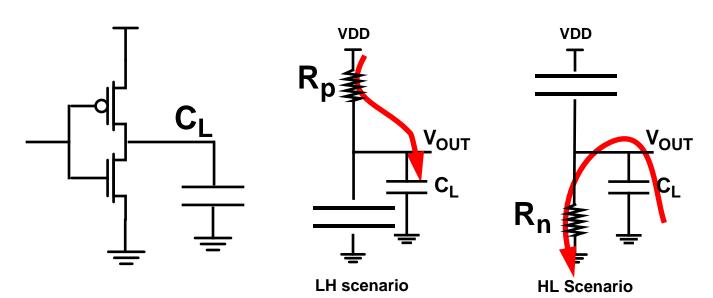

# **MOSFET Switching**

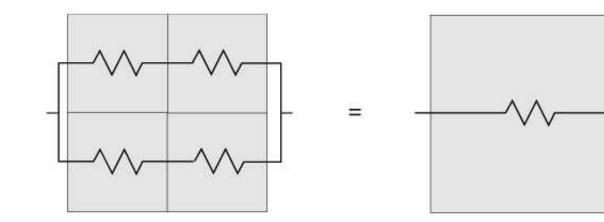

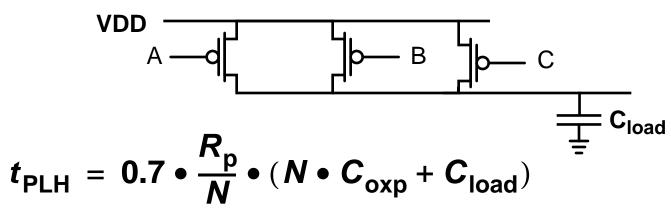

**Parallel switching (all switch at same time):**

#### Series switching (all switch at same time):

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

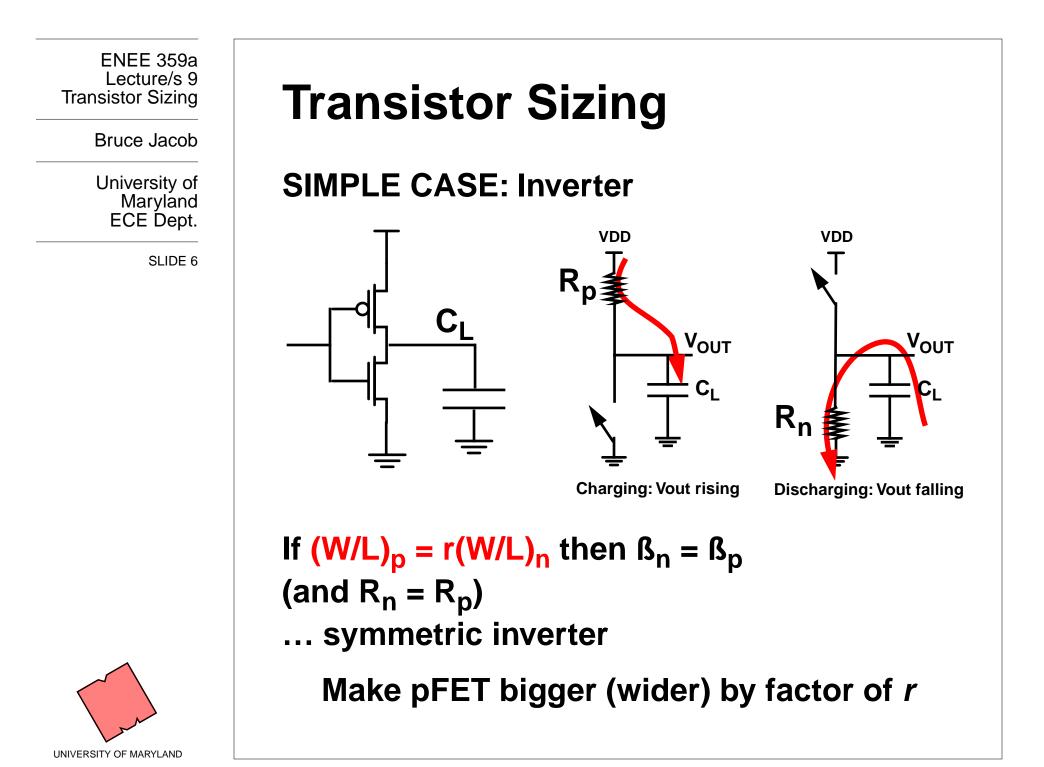

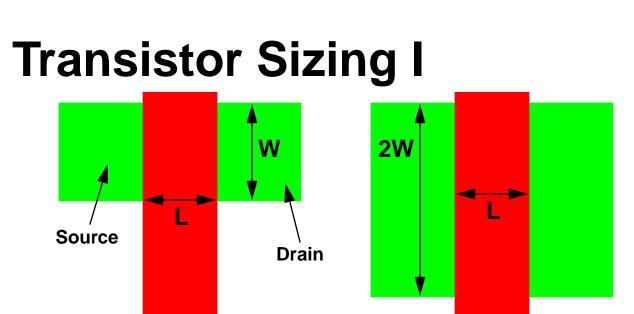

# The electrical characteristics of transistors determine the switching speed of a circuit

Need to select the aspect ratios (W/L)<sub>n</sub> and (W/L)<sub>p</sub> of every FET in the circuit

#### Define Unit Transistor (R<sub>1</sub>, C<sub>1</sub>)

- L/W<sub>min</sub>-> highest resistance (needs scaling)

- $R_2 = R_1 \div 2 \text{ and } C_2 = 2 \bullet C_1$

- Separate nFET and pFET unit transistors

- Unit devices are not restricted to individual transistors

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

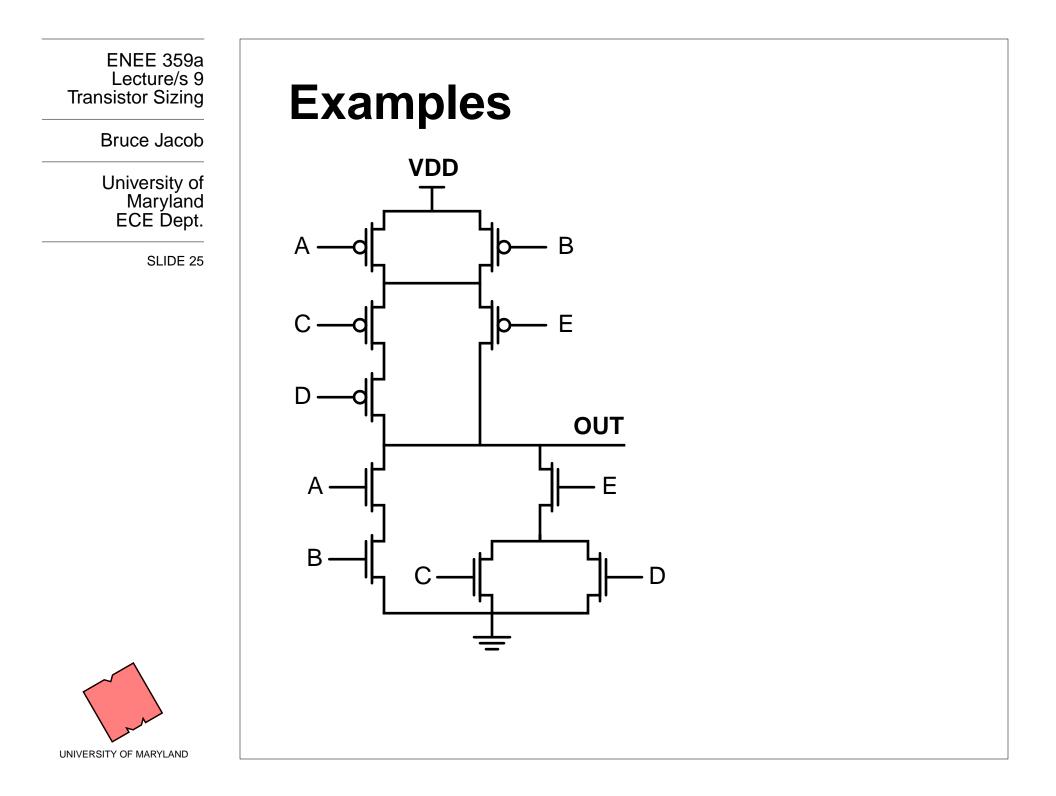

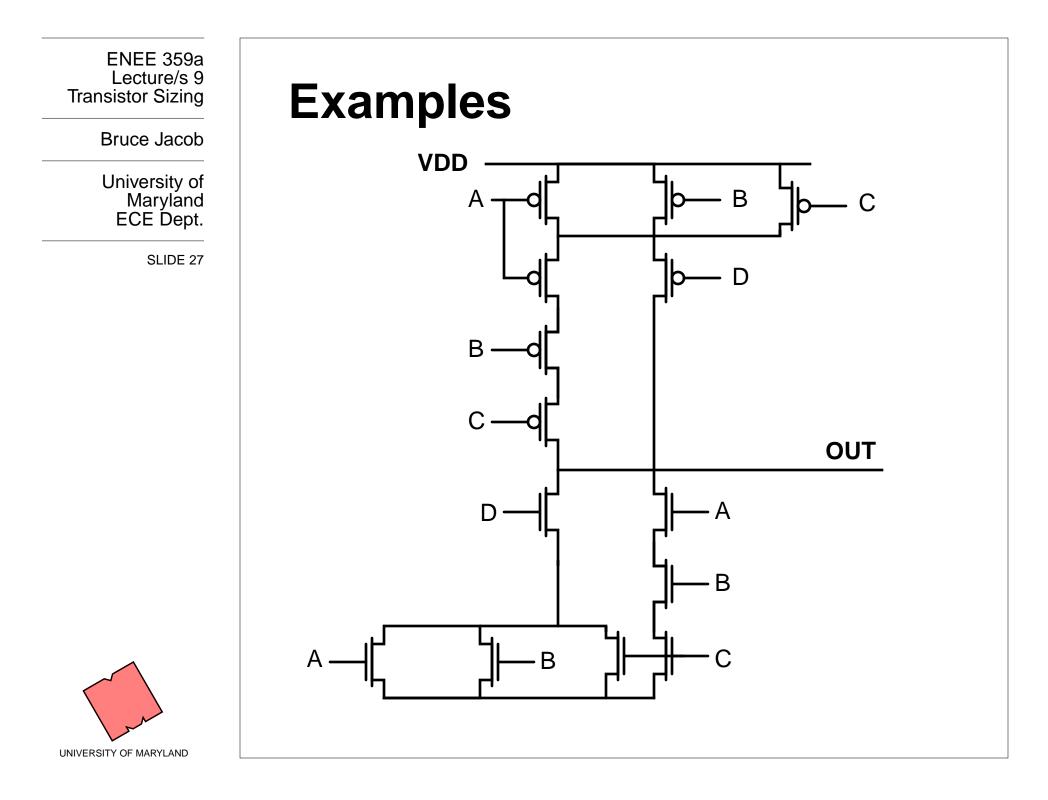

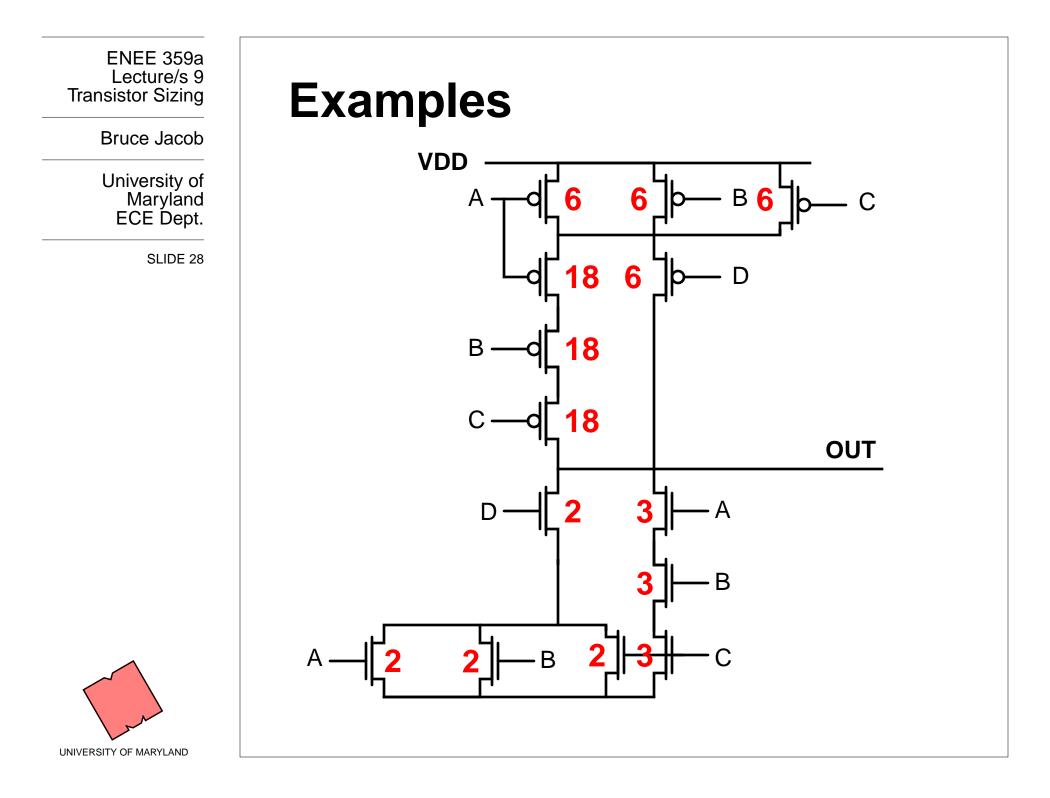

#### **ENEE 359a** Lecture/s 9 **Examples** Transistor Sizing **Bruce Jacob** VDD University of Maryland ECE Dept. VDD 6 7b-— в 6 В Α 2 ୶**ୗୄୄୄ**୳ SLIDE 26 C -— E D --12 -dl OUT Ε 2 2 A В D D 4 OUT Assuming Wp = 3Wn 2 Ε Α В D 2 UNIVERSITY OF MARYLAND

# Ways to Improve Gate Delay

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 29

## $t_p \approx (t_{pHL} + t_{pLH}) \approx [C_L \div (k'W/LV_{DD})]$ Reduce C<sub>L</sub>

- internal diffusion capacitance of the gate itself (keep the drain diffusion as small as possible)

- other terms: interconnect capacitance & fanout

#### **Increase W/L ratio of the transistor**

- the most powerful and effective performance optimization tool in the hands of the designer

- watch out for self-loading! when the intrinsic capacitance dominates the extrinsic load

## Increase V<sub>DD</sub>

- can trade-off energy for performance

- increasing V<sub>DD</sub> above a certain level yields only very minimal improvements

- reliability concerns enforce a firm upper bound on V<sub>DD</sub>

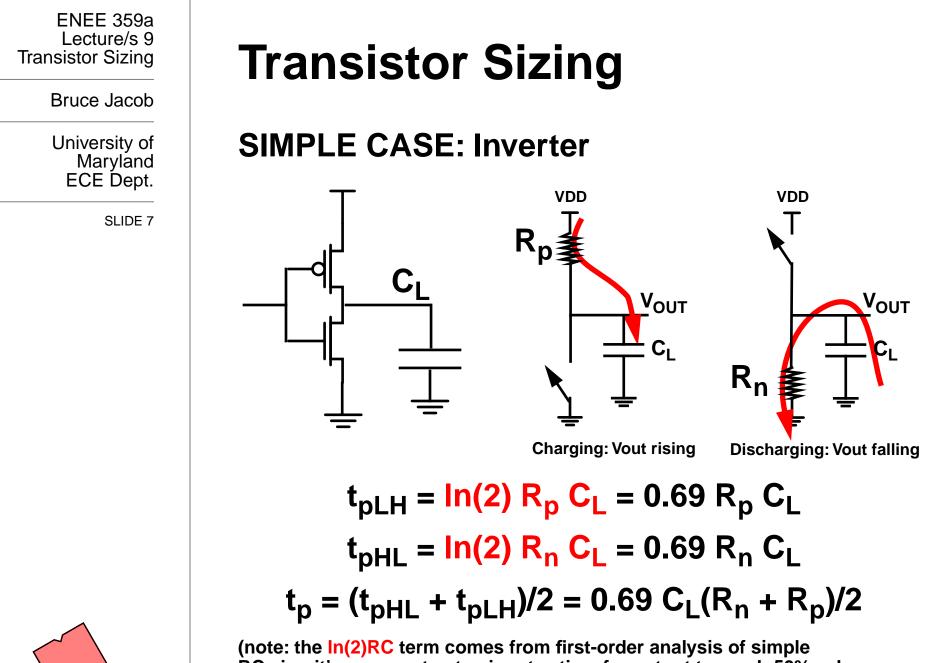

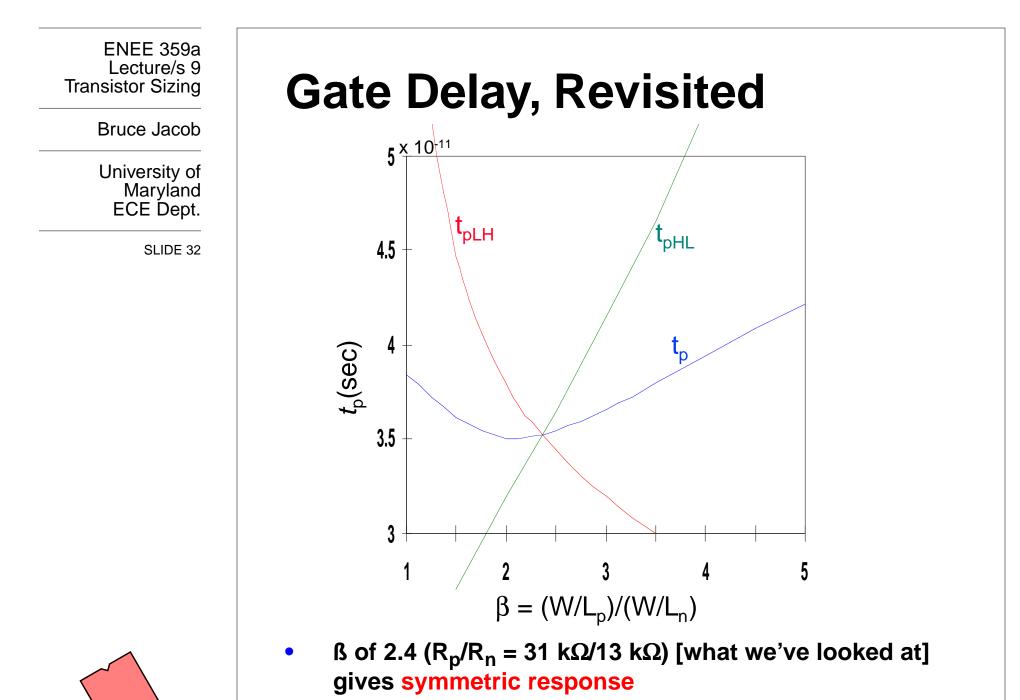

# Gate Delay, Revisited

## $t_{p} \approx (t_{pHL} + t_{pLH}) \approx 0.7 R_{ref} C_{ref} (1 + C_{ext}/SC_{iref})$

- widening the PMOS improves t<sub>pLH</sub> (R<sub>p</sub> is lower) but degrades t<sub>pHL</sub> (increases intrinsic capacitance G<sub>GD</sub> and G<sub>DB</sub>)

- widening the NMOS improves t<sub>pHL</sub> (R<sub>n</sub> is lower) but degrades t<sub>pLH</sub> (increases intrinsic capacitance G<sub>GD</sub> and G<sub>DB</sub>)

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 31

# Gate Delay, Revisited

# So far have sized the PMOS and NMOS so that the $R_{eq}$ 's match (ratio between 2 & 3.5)

- symmetrical VTC

- equal high-to-low and low-to-high propagation delays

# If speed is the only concern, reduce the width of the PMOS device!

widening the PMOS degrades t<sub>pHL</sub> due to larger parasitic capacitance (intrinsic capacitance)

$\mathsf{B} = (\mathsf{W}/\mathsf{L}_p)/(\mathsf{W}/\mathsf{L}_n)$

- r = R<sub>eqp</sub>/R<sub>eqn</sub> (resistance ratio of identically-sized PMOS and NMOS)

- $B_{opt} \approx \sqrt{r}$  if wiring capacitance negligible

• ß of 1.6 to 1.9 gives optimal performance

UNIVERSITY OF MARYLAND

# Inverter Delay

$t_p = 0.7R_{ref}C_{ref} (1 + C_{ext}/SC_{iref})$

$C_{int} = \gamma C_{g}$  $t_{p} = t_{p0} \left( 1 + \frac{C_{ext}}{\gamma C_{g}} \right)$  $t_{p} = t_{p0} \left( 1 + \frac{f}{\gamma} \right)$

Propagation time is function of ratio of external to internal capacitance

This ratio is called fan-out, f

Gamma term is function of technology,  $\gamma \approx 1$

ENEE 359a Lecture/s 9 Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 34

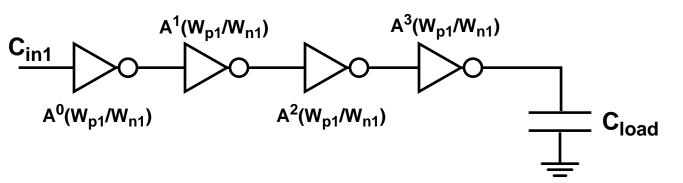

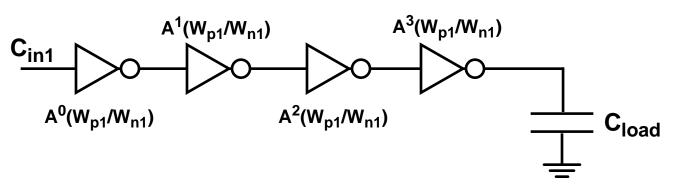

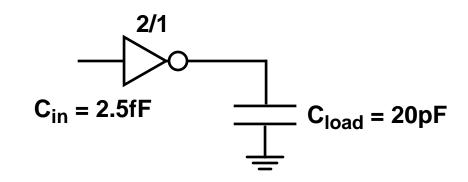

# Sizing & Big Gates

### Sizing for Large Capacitive Loads

### Supose C<sub>load</sub> large (e.g. off-chip wires)

- Scale each *inverter* (both FETs in the circuit) by a factor A (input capacitances scale by A)

- if input C to last inverter \* A = C<sub>load</sub>

(i.e., C<sub>load</sub> looks like N+1<sup>th</sup> inverter) then we have:

Input C of last inverter =  $C_{in1} A^N = C_{load}$

• Rearranging:

$$A = [C_{load} \div C_{in1}]^{1/N}$$

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 35

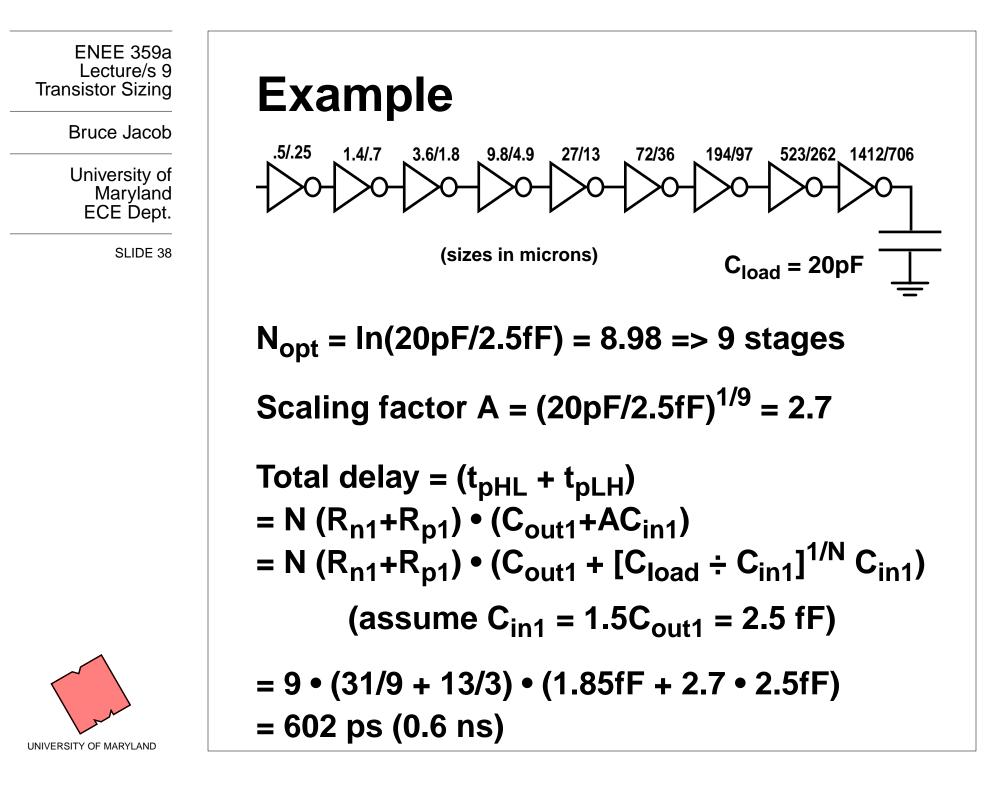

# Sizing & Big Gates

### Sizing for Large Capacitive Loads

- Capacitances increase by factor of A left to right

- Resistances decrease by factor of A left to right

- Total delay (t<sub>pHL</sub> + t<sub>pLH</sub>):

$$(R_{n1}+R_{p1}) \cdot (C_{out1}+AC_{in1}) +$$

$(R_{n1}+R_{p1})/A \cdot (AC_{out1}+A^{2}C_{in1}) + ...$

$= N (R_{n1}+R_{p1}) \cdot (C_{out1}+AC_{in1})$

Find optimal chain length:

$$N_{opt} = In(C_{load} \div C_{in1})$$

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 36

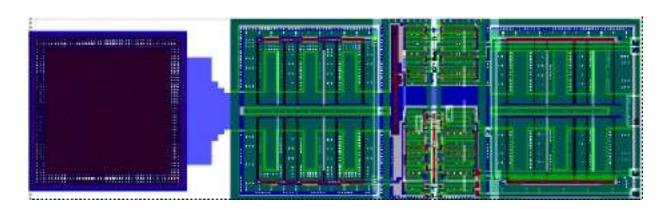

# Sizing & Big Gates

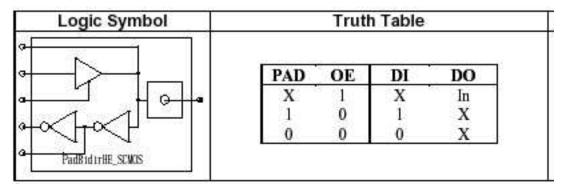

I/O Pad: large structures are ESD diodes and inverter chains (scale: pad is ~65 µm)

## Example

Load is ~8000x that of single inverter's input capacitance: find optimal solution.

**ENEE 359a** Lecture/s 9 **Transistor Sizing**

**Bruce Jacob**

University of Maryland ECE Dept.

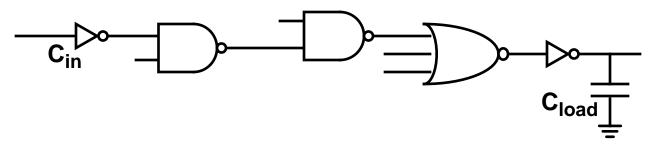

# Generalize: Logical Effort

Want to find minimum delay for chains:

**Main Points:**

- Path length is (maybe) fixed; find scaling

- Want constant scaling factor along path

[ this gives same gate effort at each stage ]

- RC delay of a gate uses sum of internal C (its own C<sub>out</sub>) and input of next gate (C<sub>in</sub>)

Bruce Jacob University of Want to

University of Maryland ECE Dept.

ENEE 359a Lecture/s 9

Transistor Sizing

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 40

# Definitions

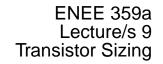

### g = Gate-level logical effort

= ratio of its input capacitance to that of INVERTER

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 41

# Definitions

Total Path Effort H = GFB

Optimal gate effort  $h = \frac{N}{H}$

## **G** = Path Logical Effort

Bruce Jacob

University of Maryland ECE Dept.

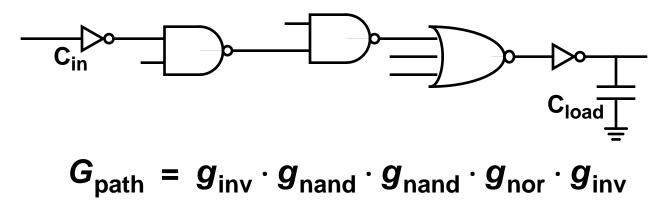

SLIDE 42

# Definitions

Total Path Effort H = GFB

Optimal gate effort  $h = \frac{N}{H}$

**F** = Effective Fan-Out of Chain

Also called *Electrical Effort*

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 43

# Definitions

Total Path Effort H = GFB

Optimal gate effort  $h = \frac{N}{H}$

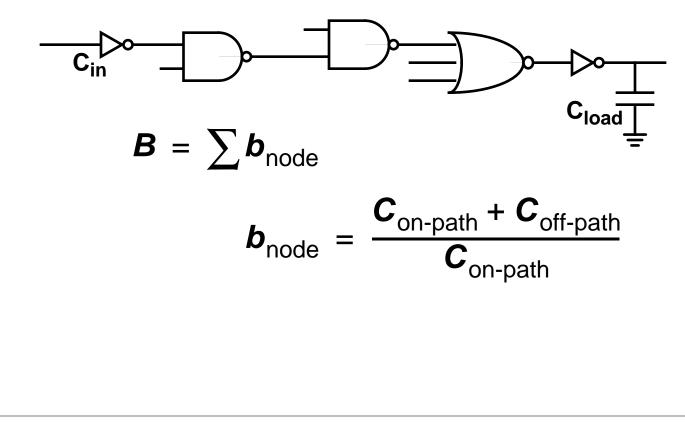

#### **B** = Path Branching Effort

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 44

# Definitions

Total Path Effort H = GFB

Optimal gate effort  $h = \frac{N}{H}$

**Redefine inverter delay:**

$$t_{\rm p} = t_{\rm p0} \left(1 + \frac{f}{\gamma}\right) \implies t_{\rm p} = t_{\rm p0} \left(p + \frac{fg}{\gamma}\right)$$

**Total delay through path:**

$$D = t_{p0} \sum \left( p_i + \frac{f_i g_i}{\gamma} \right)$$

Minimum delay through path:  $D = t_{p0} \left( \sum p_i + \frac{N^N \sqrt{H}}{\gamma} \right)$

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 45

# Definitions

Total Path Effort H = GFB

Optimal gate effort  $h = \frac{N}{H}$

Gate effort **h**<sub>i</sub> = **g**<sub>i</sub>**f**<sub>i</sub>

Sizing s<sub>i</sub> for gate i in chain:

$$\mathbf{s}_{i} = \left(\frac{\mathbf{g}_{1}\mathbf{s}_{1}}{\mathbf{g}_{i}}\right) \prod_{j=1}^{i-1} \left(\frac{f_{j}}{b_{j}}\right)$$

Bruce Jacob

University of Maryland ECE Dept.

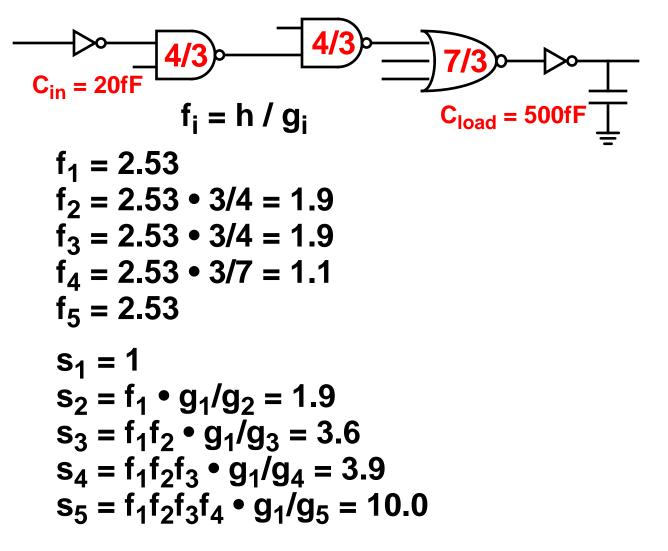

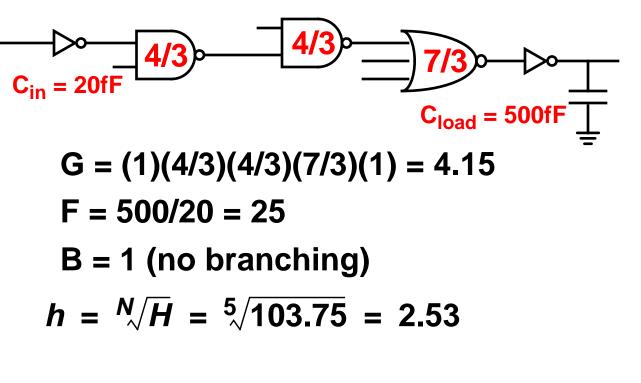

SLIDE 46

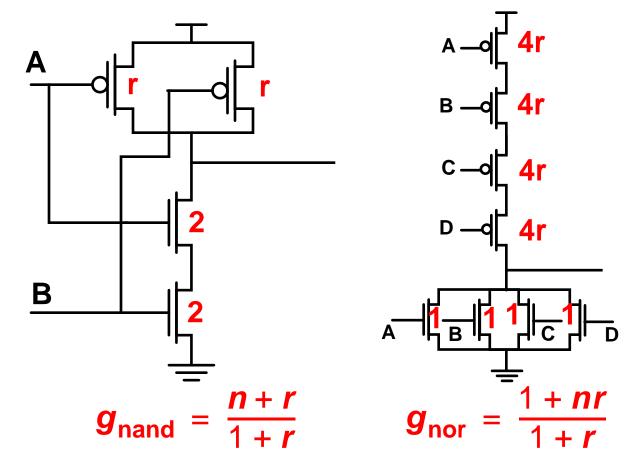

# Analysis

Find minimum delay for chain (assume r=2):

Bruce Jacob

University of Maryland ECE Dept.

SLIDE 47

# Analysis

Find minimum delay for chain (assume r=2):