1.7 points

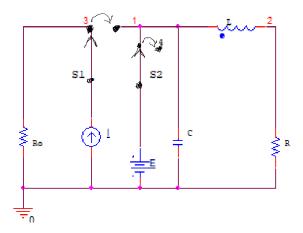

The following circuit is assumed to have existed for all time. At t=0 the switch S1 switches from node 3 to node 1 (connecting I to the RLC circuit) and S2 opens (switching from node 1 to node 4, thus disconnecting E). I and E are constant, DC, current and voltage, respectively; R, Ro, L and C are positive element values.

- a) (3 points) Set up the (second order) differential equation for  $v_1(t)$  for t>0 [where  $v_1$  is the capacitor node voltage measured with respect to ground].

- b) (3 points) Find the following capacitor voltage and current values immediately before and after switching,  $v_1(0-)$ ,  $Cdv_1/dt(0-)$  and  $v_1(0+)$ ,  $Cdv_1/dt(0+)$ .

- c) (1 point) Give the final values  $v_1(\infty)$  and inductor current  $i_L(\infty)$  [entering the dot].

2. 6 points

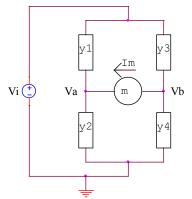

In the following bridge circuit the meter in the center is an amp-meter with input resistance of 0 Ohms. Vi is the voltage of the voltage source and the four branches are described by their admittances,  $y_i$ , i=1, 2,3,4. The current Im in the meter is known to be given by

$Im = [(y_2 \cdot y_3 - y_1 \cdot y_4)/(y_1 + y_2 + y_3 + y_4)]Vi$

- a) (3 points) Find the relationship between the y<sub>i</sub> such that the bridge is in balance, that is when Im=0.

- b) (3 points) If  $y_1$  at balance is perturbed to become  $y_5=y_1+\Delta y_1$  [where  $y_1$  is as in a)] and  $y_2$  and  $y_3$  are unperturbed, find the perturbation  $\Delta y_4$  of  $y_4$  such that  $y_4+\Delta y_4$ returns the bridge to balance.

3.7 points

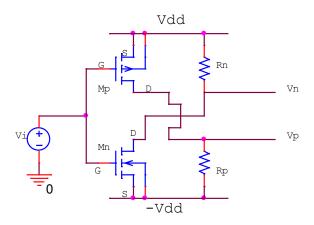

When the following NMOS transistor is in saturation (that is when  $V_{DS} \ge V_{GS}$ -Vth) its drain current is described by (k and the threshold voltage Vth are both positive)

$$I_D = k(V_{GS} - Vth)^2$$

[for NMOS]

Assume also that the PMOS is completely complementary, that is (with the same k and Vth) so that

$I_S = k(V_{SG}-Vth)^2$  [for PMOS]

(here the source current  $I_S$  and the drain current  $I_D$  are taken as positive when going into the source, S, and the drain, D, respectively)

The bias voltage Vdd is large enough to make the circuit operational [note the presence of the negative bias].

a) (3 points) When the input voltage is zero, Vi=0, find the maximum resistance value, Rn=Rmax [in terms of k, Vth and Vdd], such that the NMOS transistor is in saturation.

b) (3 points) Again at Vi=0 and when Rn and Rp are both smaller than Rmax, find the output difference voltage, Vdiff=Vn-Vp, (again in terms of k, Vth and Vdd) [Vn and Vp are measured with respect to ground].

c) (1 point) Is it possible to design the circuit to obtain Vdiff = 0 when Vi=0? Explain your answer.

b) The new belonce

$$y_{3}y_{3} = (y_{1} + \Delta y_{1})(y_{4} + \Delta y_{4}) = y_{1}y_{4} + [y_{4}Ay_{1} + y_{1}Ay_{1} + Ay_{1}Ay_{1}]$$

$$\Rightarrow [\cdot] term = 0 \Rightarrow 0 = y_{4}\Delta y_{1} + (y_{1} + \Delta y_{1}) \cdot \Delta y_{4} \Rightarrow \Delta y_{4} = \frac{-\Delta y_{1}y_{4}}{y_{1} + \Delta y_{1}}$$

c) We need

$$V_{n}-V_{p} = 0 \Rightarrow (E_{n}+R_{p}) \cdot k(V_{dd}-V_{dh})^{n} = 2V_{dd} \quad de \quad R_{n}+R_{p} = \frac{4V_{dd}}{R(V_{dd}-V_{dh})^{2}}$$

The mappingum  $(R_{m}+R_{p}) = 2K_{map} = \frac{2V_{dd}}{R(V_{dd}-V_{dd})^{2}} + \frac{2V_{dd}}{R(V_{dd}-V_{dd})^{2}}$

as this speeds by  $\frac{2V_{dh}}{R(V_{dd}-V_{dd})^{2}}$  the amount needed to force  $V_{m}-V_{p} = 0$

we can choose  $R_{p} = R_{p} = R_{map} - \frac{V_{dd}}{R(V_{dd}-V_{dd})^{2}}$