## Digital Logic Design ENEE 244-010x

Lecture 15

#### Announcements

- Homework 7 due Wednesday 11/4

- Coming up: Midterm on 11/11

- Topics for Midterm posted online

- Review problems will be posted by Tuesday night

# Agenda

- Last time:

- Decimal Adders (5.2)

- Comparators (5.3)

- Decoders (5.4)

- Encoders (5.5)

- Multiplexers (5.6)

- This time:

- Logic Design with Decoders and Multiplexers (5.4, 5.6)

- Start Programmable Logic Devices (PLD) (5.7)

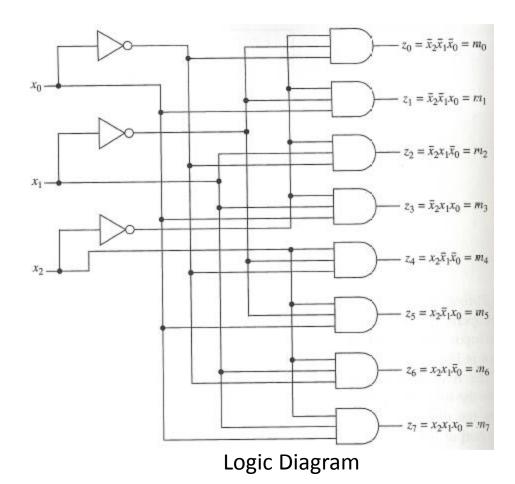

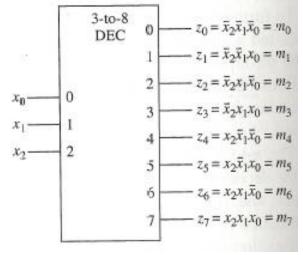

### Logic Design Using Decoders

Symbol

| Inputs            | Outputs |       |       |       |       |       |                |    |

|-------------------|---------|-------|-------|-------|-------|-------|----------------|----|

| $x_2 \ x_1 \ x_0$ | $z_0$   | $z_1$ | $z_2$ | $z_3$ | $z_4$ | $z_5$ | z <sub>6</sub> | Z7 |

| 0 0 0             | 1       | 0     | 0     | 0     | 0     | 0     | 0              | 0  |

| 0 0 1             | 0       | 1     | 0     | 0     | 0     | 0     | 0              | 0  |

| 0 1 0             | 0       | 0     | 1     | 0     | 0     | 0     | 0              | 0  |

| 0 1 1             | 0       | 0     | 0     | 1     |       | 0     | 0              | 0  |

| 1 0 0             | 0       | 0     | 0     | 0     | 1     | 0     | 0              | 0  |

| 1 0 1             | 0       | 0     | 0     | 0     | 0     | 1     | 0              | 0  |

| 1 1 0             | 0       | 0     | 0     | 0     | 0     | 0     | 1              | 0  |

| 1 1 1             | 0       | 0     | 0     | 0     | 0     | 0     | 0              | 1  |

| Truth Tabla       |         |       |       |       |       |       |                |    |

Truth Table

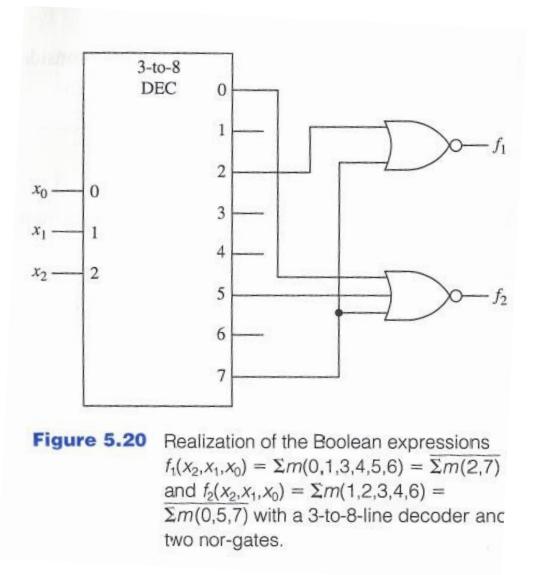

# Logic Design Using Decoders

- An n-to- $2^n$  line decoder is a minterm generator.

- By using or-gates in conjunction with an *n*-to-2<sup>*n*</sup> line decoder, realizations of Boolean functions are possible.

- Do not correspond to minimal sum-of-products.

- Are simple to produce. Particularly convenient when several functions of the same variable have to be realized.

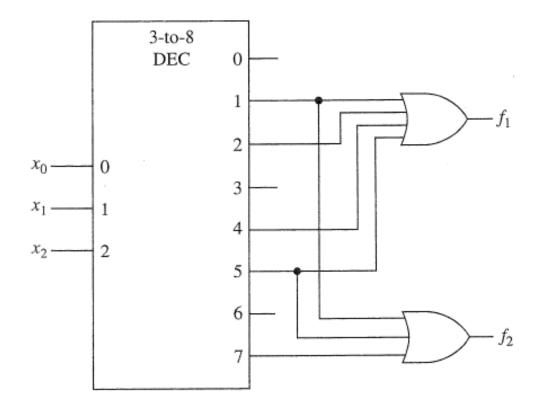

## Minterms using OR Gates

**Figure 5.19** Realization of the Boolean expressions  $f_1(x_2, x_1, x_0) = \Sigma m(1, 2, 4, 5)$  and  $f_2(x_2, x_1, x_0) = \Sigma m(1, 5, 7)$  with a 3-to-8-

## Minterms using NOR Gates

| X | у | Z | f     |

|---|---|---|-------|

| 0 | 0 | 0 | $f_0$ |

| 0 | 0 | 1 | $f_1$ |

| 0 | 1 | 0 | $f_2$ |

| 0 | 1 | 1 | $f_3$ |

| 1 | 0 | 0 | $f_4$ |

| 1 | 0 | 1 | $f_5$ |

| 1 | 1 | 0 | $f_6$ |

| 1 | 1 | 1 | $f_7$ |

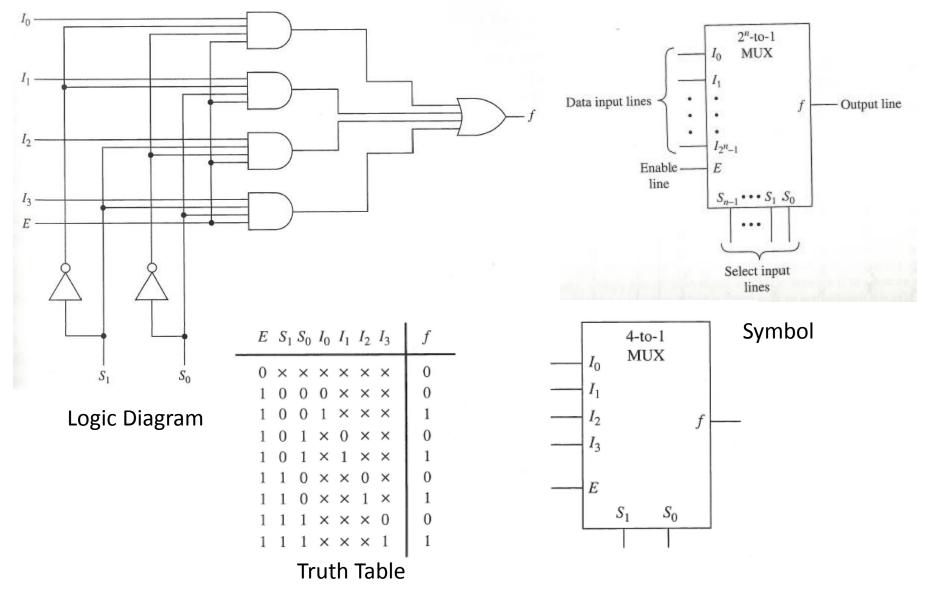

The Boolean expression corresponding to this truth table can be written as:

$$f(x, y, z) = f_0 \cdot \overline{x} \, \overline{y} \, \overline{z} + f_1 \cdot \overline{x} \, \overline{y} \, z + f_2 \cdot \overline{x} y \overline{z} + f_3 \cdot \overline{x} y z + f_4 \cdot x \overline{y} \, \overline{z} + f_5 \cdot x \overline{y} z + f_6 x y \overline{z} + f_7 \cdot x y z.$$

• The Boolean expression corresponding to this truth table can be written as:

$f(x, y, z) = f_0 \cdot \overline{x} \, \overline{y} \, \overline{z} + f_1 \cdot \overline{x} \, \overline{y} \, z + f_2 \cdot \overline{x} \, \overline{y} \, \overline{z} + f_3 \cdot \overline{x} \, \overline{y} \, z + f_4 \cdot x \, \overline{y} \, \overline{z} + f_5 \cdot x \, \overline{y} \, z + f_6 \, x \, \overline{y} \, \overline{z} + f_7 \cdot x \, \overline{y} \, z.$

• The Boolean expression for an 8-to-1-line multiplexer is:

$$f = (I_0 \overline{S}_2 \overline{S}_1 \overline{S}_0 + I_1 \overline{S}_2 \overline{S}_1 S_0 + I_2 \overline{S}_2 S_1 \overline{S}_0 + I_3 \overline{S}_2 S_1 S_0 + I_4 S_2 \overline{S}_1 \overline{S}_0 + I_5 S_2 \overline{S}_1 S_0 + I_6 S_2 S_1 \overline{S}_0 + I_7 S_2 S_1 S_0).$$

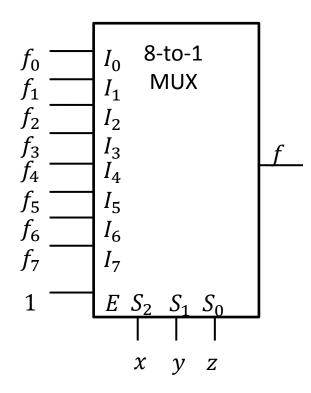

- If E is logic-1 then the latter is transformed into the former by replacing  $I_i$  with  $f_i$ ,  $S_2$  with x,  $S_1$  with y, and  $S_0$  with z.

- Placing x, y, z on the select lines  $S_2, S_1, S_0$ , respectively and placing the functional values  $f_i$  on data input lines  $I_i$ .

### Example:

| x | y | Z | f |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

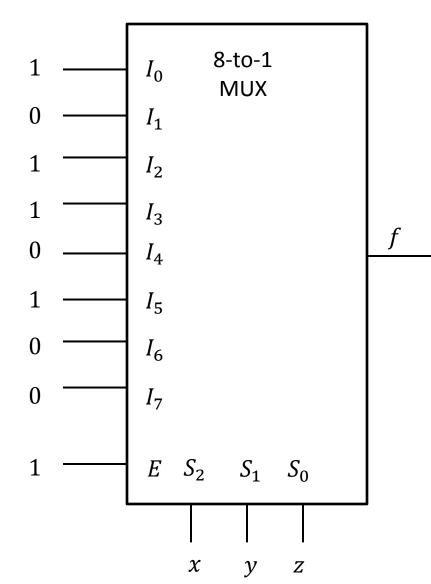

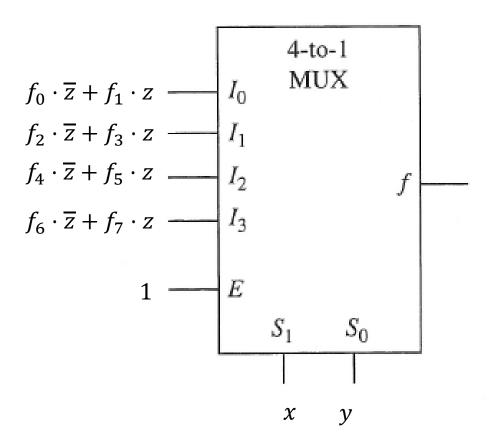

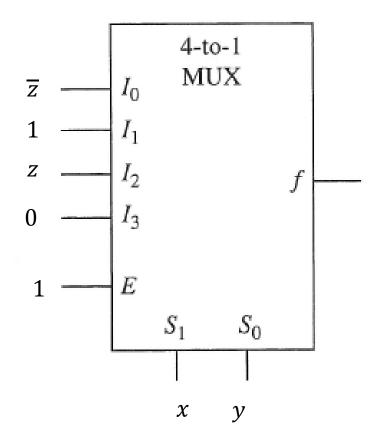

- If at least one input variable of a Boolean function is available in both its complemented and uncomplemented form, any *n*-variable function is realizable with a  $2^{n-1}$ -to-1-line multiplexer.

- For the case of a 3-variable function, only a 4-to-1 multiplexer is needed.

•

$$f(x, y, z) = f_0 \cdot \overline{x} \, \overline{y} \, \overline{z} + f_1 \cdot \overline{x} \, \overline{y} \, z + f_2 \cdot \overline{x} y \overline{z} + f_3 \cdot \overline{x} y z + f_4 \cdot x \overline{y} \, \overline{z} + f_5 \cdot x \overline{y} z + f_6 x y \overline{z} + f_7 \cdot x y z$$

$$= (f_0 \cdot \overline{z} + f_1 \cdot z) \overline{x} \, \overline{y} + (f_2 \cdot \overline{z} + f_3 \cdot z) \overline{x} y$$

$$+ (f_4 \cdot \overline{z} + f_5 \cdot z) x \overline{y} + (f_6 \cdot \overline{z} + f_7 \cdot z) x y$$

• When E = 1, 4-to-1 Multiplexer has the form  $I_0\overline{S}_1\overline{S}_0 + I_1\overline{S}_1S_0 + I_2S_1\overline{S}_0 + I_3S_1S_2$

- $f(x, y, z) = (f_0 \cdot \overline{z} + f_1 \cdot z)\overline{x} \, \overline{y} + (f_2 \cdot \overline{z} + f_3 \cdot z)\overline{x}y + (f_4 \cdot \overline{z} + f_5 \cdot z)x\overline{y} + (f_6 \cdot \overline{z} + f_7 \cdot z)xy$ 4-to-1 Multiplexer has the form  $f = I_0\overline{S}_1\overline{S}_0 + I_1\overline{S}_1S_0 + I_2S_1\overline{S}_0 + I_3S_1S_2$  Realization of f(x, y, z) is obtained by placing the x and y variables on the  $S_1, S_0$  select lines, the

- single variable functions  $f_i \cdot \overline{z} + f_j \cdot z$  on the data input lines and let E = 1.

- Note:  $f_i \cdot \overline{z} + f_j \cdot z$  reduce to 0,1,*z* or  $\overline{z}$ .

### Example

### Example

| x | y | Z | f |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

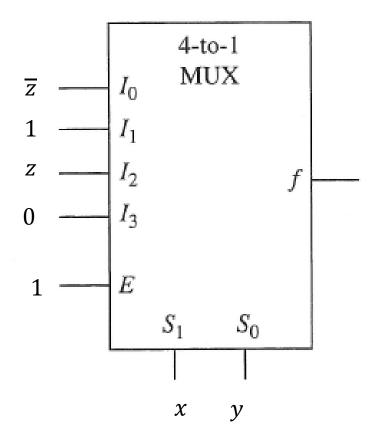

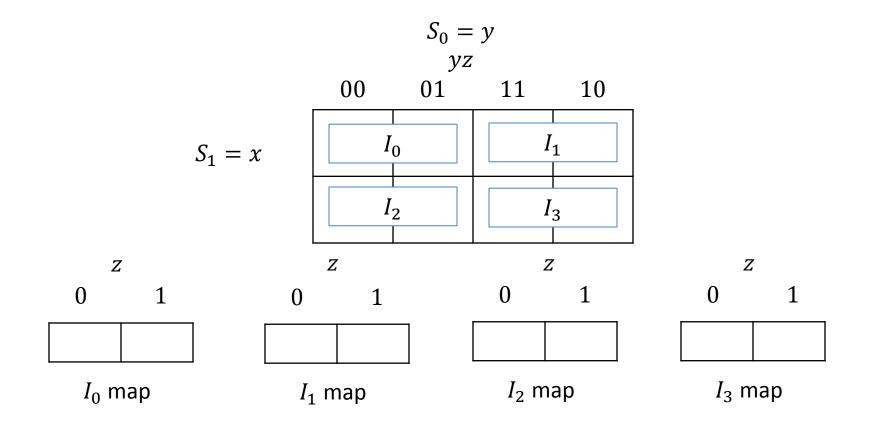

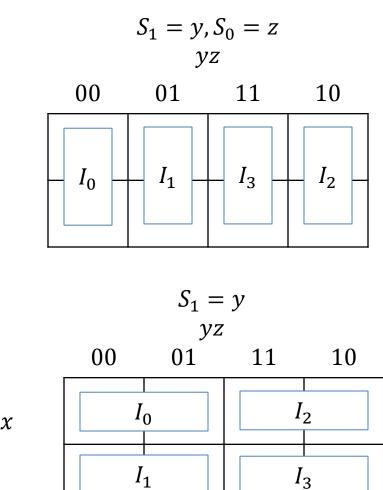

## Logic Design with Multiplexers and Kmaps

- Consider 3-variable Karnaugh map. Assume x is placed on the S<sub>1</sub> line and y is placed on the S<sub>0</sub> line.

- We get that the output is:  $I_0 \overline{x} \overline{y} + I_1 \overline{x} y + I_2 x \overline{y} + I_3 x y$

- $I_0 \overline{x} \overline{y}$  corresponds to those cells in which x = 0, y = 0

- $I_1 \overline{x} y$  corresponds to those cells in which x = 0, y = 1

- $I_2 x \overline{y}$  corresponds to those cells in which x = 1, y = 0

- $I_3 xy$  corresponds to those cells in which x = 1, y = 1

#### K-map representation

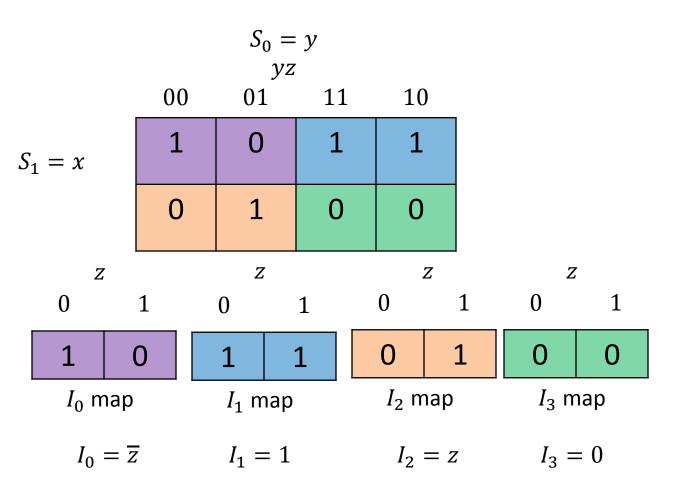

## Example

| x | y | Z | f |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

### Realization

| x | y | Z | f |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

#### **Alternative Structures**

Note that order of variables on input lines matters!

X

$$S_0 = z$$

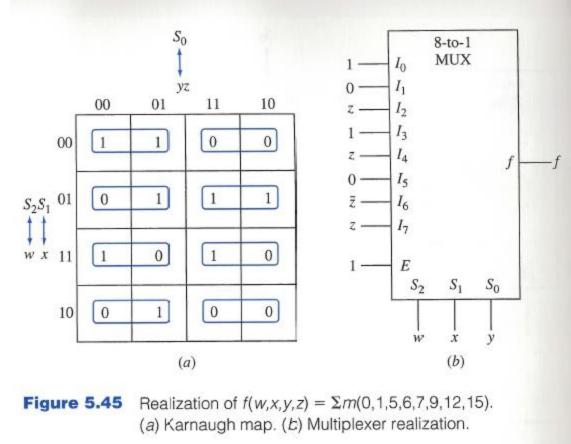

## 8-to-1-line multiplexers and 4-variable Boolean functions

- Can do the same thing, three variables are placed on select lines, inputs to the data lines are single-variable functions.

- Example:

## Can we do better?

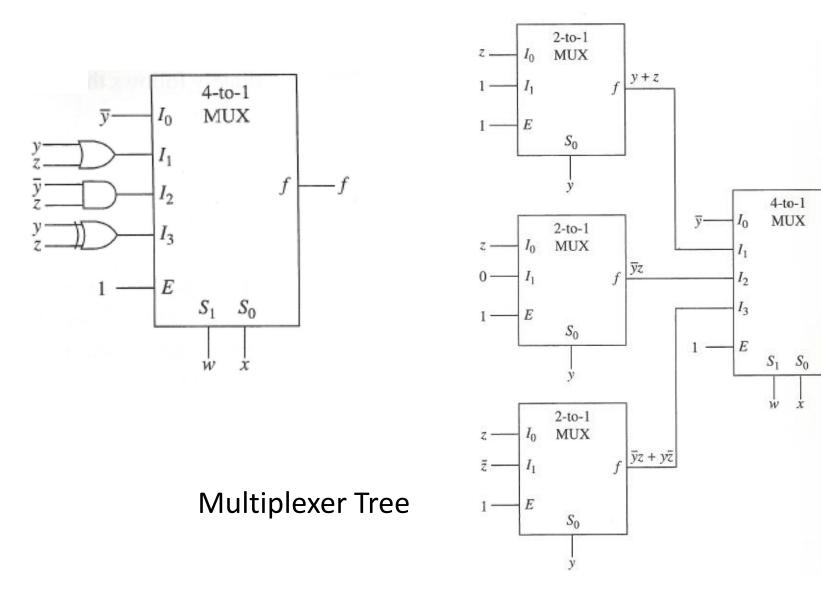

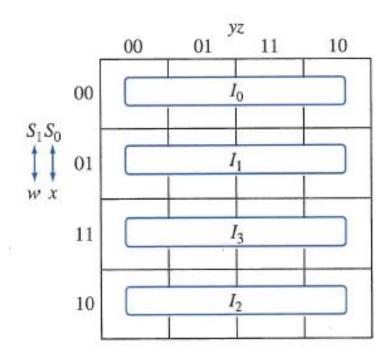

- By allowing realizations of m-variable functions as inputs to the data input lines,  $2^n$ to-1-line multiplexers can be used in the realization of (n + m)-variable functions.

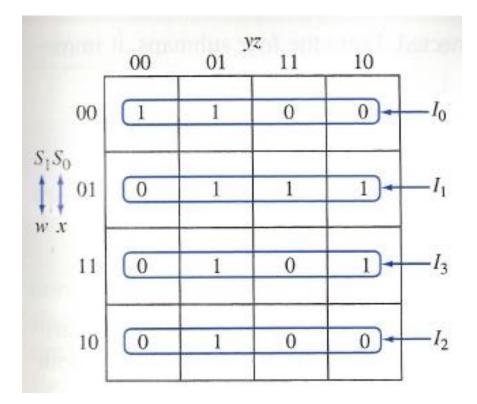

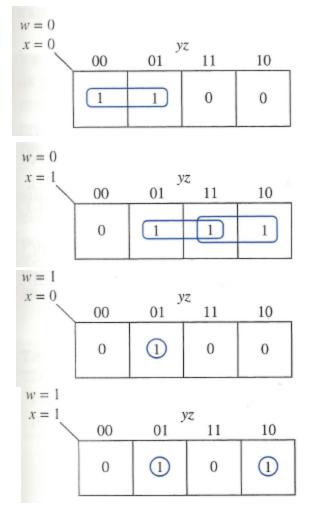

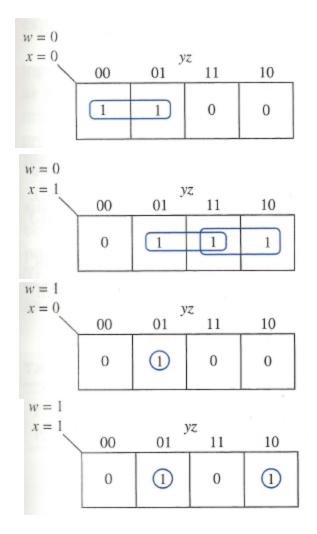

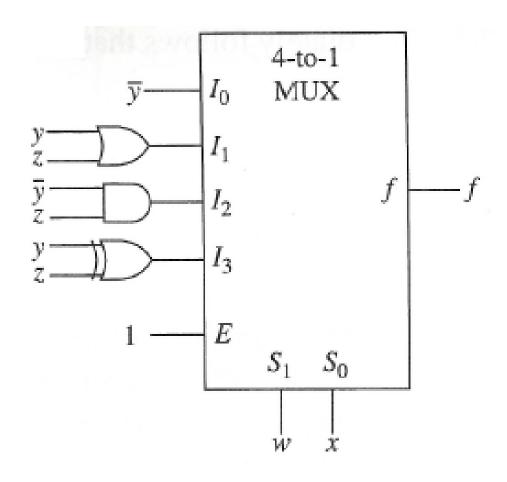

- E.g.: input variables w and x are applied to the S<sub>1</sub>, S<sub>0</sub> select inputs. Functions of the y and z variables appear at the data input lines.

### K-map Structure

Figure 5.46 Using a four-variable Karnaugh map to obtain a Boolean function realization with a 4-to-1-line multiplexer.

#### Example:

$f(x, y, z) = \sum m(0, 1, 5, 6, 7, 9, 13, 14)$

## Example

## Example