## Class Exercise—Latches and Flip-Flops

## 11/16/15

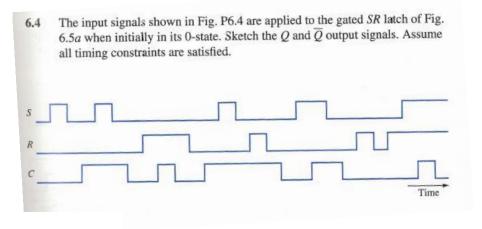

6.5 The input signals shown in Fig. P6.5 are applied to the gated D latch of Fig. 6.6a when initially in its 0-state. Sketch the Q and Q output signals. Assume all timing constraints are satisfied.

## Class Exercise—Latches and Flip-Flops 11/16/15

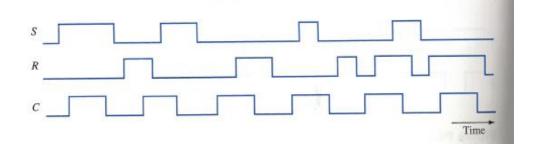

**6.6** The input signals shown in Fig. P6.6 are applied to the master-slave *SR* flipflop of Fig. 6.12*a* when initially in its 0-state. Sketch the  $Q_M$ ,  $\overline{Q}_M$ ,  $Q_S$ , and  $\overline{Q}_S$  output signals. Assume all timing constraints are satisfied.

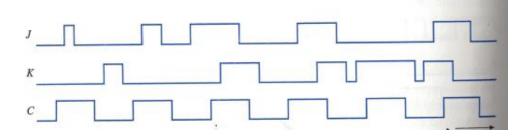

6.7 The input signals shown in Fig. P6.7 are applied to the master-slave JK flipflop of Fig. 6.14*a* when initially in its 0-state. Sketch the  $Q_M$  and  $Q_S$  output signals. Assume all timing constraints are satisfied.