News Story

$4.96M for Maryland researchers in DARPA AISS semiconductor security project

Cybersecurity threats don’t just come from clicking a link in the wrong email. In recent years cybersecurity threats are being directed against the integrated circuit (IC) chips that run every computer—from top secret super computers, to your laptop, to Internet of Things devices like your “smart” TV or thermostat. Today, a well-placed cyberattack on IC chips could potentially impact billions of devices. But currently, there are no widely used common tools, methods or solutions to make designing and manufacturing IC chips more secure.

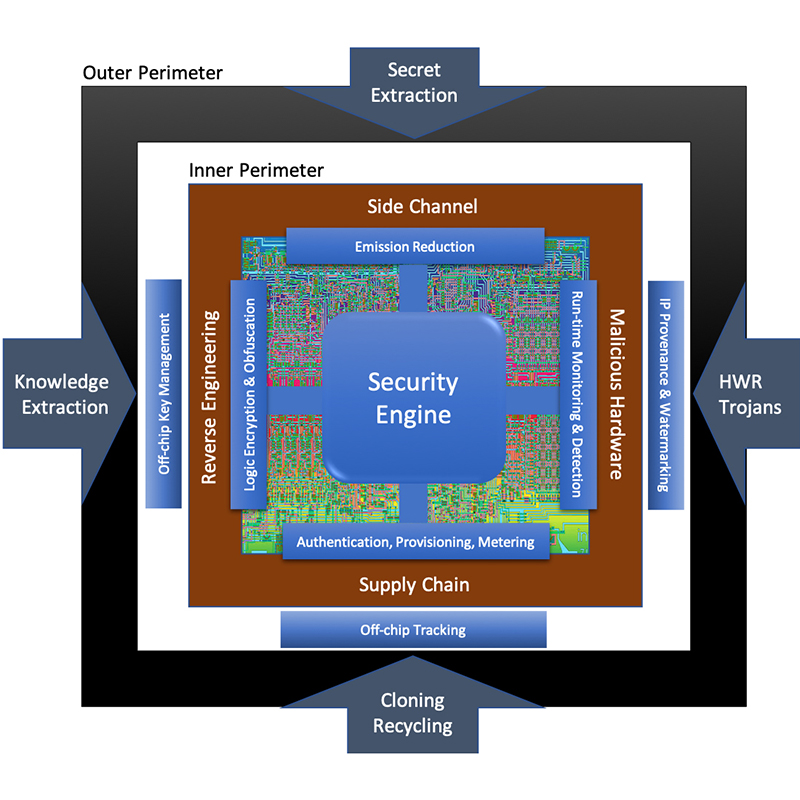

The University of Maryland is receiving $4.96 million in funding as part of a new four-year, multi-team Defense Advanced Research Projects Agency (DARPA) project called Automated Implementation of Secure Silicon (AISS), which is aimed at making scalable on-chip security pervasive. The objective of DARPA’s AISS is to develop a design tool and intellectual property ecosystem—including tool vendors, chip developers, IP licensers, and the open source community—capable of automating the process of adding security into integrated circuits.

AISS will allow security to be inexpensively incorporated into chip designs with minimal effort and expertise, ultimately making scalable on-chip security ubiquitous. The project seeks to create a novel, automated chip design flow that will allow the security mechanisms to scale consistently with the goals of the design.

Two teams, led by Synopsys and Northrop Grumman, will be developing security technology that can address four attack surfaces relevant to chip design: side channel attacks, reverse engineering attacks, supply chain attacks, and malicious hardware attacks. Their efforts will help chip designers assess which defense mechanisms are most appropriate based on the potential attack surface and the likelihood of a compromise. Each of these teams will design a chip security engine.

A third team, led by the Applied Research Laboratory for Intelligence and Security (ARLIS), includes University of Maryland researchers in the Institute for Systems Research (ISR), the Department of Electrical and Computer Engineering (ECE), the Fraunhofer USA Center for Experimental Software Engineering (Fraunhofer USA CESE), as well as a group from New York University (NYU)—will try to break through the security and discover key attributes of the IC chip being protected.

Warren Savage, a visiting researcher at ARLIS, is the principal investigator for this Independent Verification and Validation (IV&V) aspect of the overall AISS program.

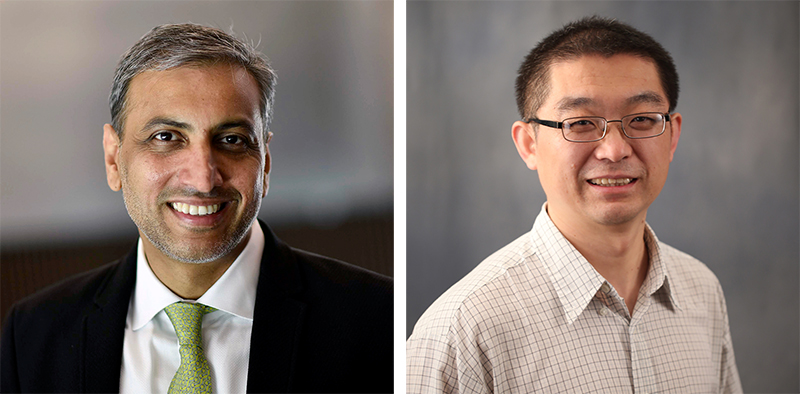

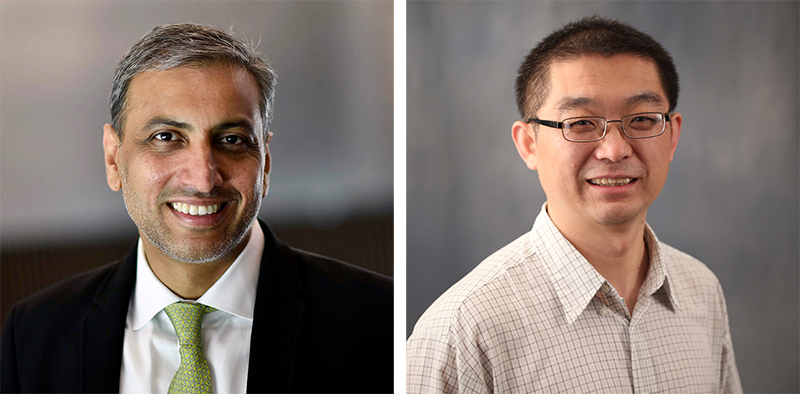

Maryland researchers led by ISR Director and Professor Ankur Srivastava (ECE/ISR) and Professor Gang Qu (ECE/ISR) will attempt to exploit hardware trojan and side channel attacks, and Srivastava will validate obfuscation techniques. Hardware trojans are malicious modifications of IC circuitry that can change a chip’s function, cause leakage of sensitive information, or contribute to denial of service.

Srivastava will assess the AISS design flow’s resilience against the insertion of hardware trojans into chip designs and the interoperability of third-party obfuscation/locking technology with AISS design tools. His team will insert a variety of types of hardware trojans and evaluate AISS on how well it detects their presence. Srivastava is also validating obfuscation techniques.

Qu’s group will use side channel attacks to try to break through the AISS security engine to reveal secret keys. These attacks are intended to extract secret information from a chip by targeting weaknesses in the physical implementation of a chip. Qu will use known side channel attacks such as power, timing, electromagnetic leakage, cache and scan chains. He will assess the AISS design flow’s ability to detect and suppress these kinds of attacks.

The Fraunhofer USA CESE team, led by its Executive Director and ISR-affiliated Professor Adam Porter (CS/UMIACS), will address supply chain concerns. They will conduct blockchain and Asset Management Infrastructure attacks and verify interoperability of new Hyperledger nodes associated with the AISS Certificate Authority.

NYU’s Professor Ramesh Karri (ECE) and his group will conduct reverse engineering attacks using the latest attack methodologies, including a family of Boolean satisfiability checking (SAT) methods in an attempt to unlock designs that have been protected using with logic locking and design obfuscation methods. Karri and his team also will perform interoperability testing of its own logic locking/obfuscation technology, ASSURE, with the AISS design tools.

In addition, the University of Maryland is also standing up and operating a cloud-based design environment to allow all fifteen AISS performer companies to collaborate with each other in a secure manner. A custom cloud architecture for the program was developed by ARLIS and deployed on Google Cloud Platform with the assistance of Google’s partner SADA Systems Inc.

“AISS represents a real opportunity to be a game-changer in how we design for security in IC design,” Warren Savage says. “Maryland’s participation in the AISS program is emblematic of its unique capabilities in bringing together the leading researchers and technologists across the country to solve challenging real-world problems facing both the commercial and defense industrial bases.”

Published December 1, 2020